## **Project Summary**

Contract Number: NAS2-01049 Proposal Number: 24.01-8755

Proposal Title: Autonomously Self-Repairing Circuits

#### Summary (Limit 400 words):

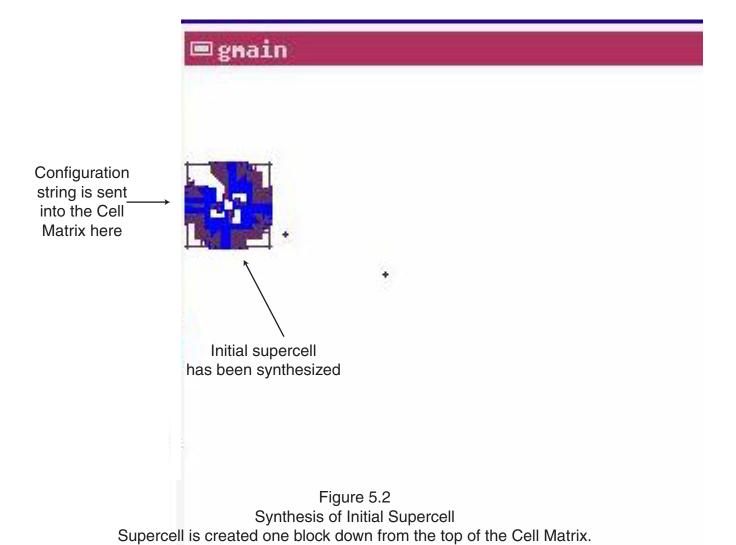

The purpose of our Phase-I research was to develop a methodology for implementing \*autonomously self-repairing circuits\*, based on a novel self-configurable architecture called the Cell Matrix. In order for the implemented circuit to be able to repair itself, it must contain not only information about itself, but also the necessary machinery for testing the underlying hardware, detecting and isolating faults, and working around faulty regions. The proposed approach involved designing a "supercell" to perform all these tasks. Each supercell contains a "genome" which specifies the target circuit. Supercells test the hardware for faults, isolate faulty regions from fault-free ones, configure new supercells, determine how to re-implement the target circuit given the current faults, and ultimately wire themselves together to implement the target circuit. This entire process is started by supplying a single, fixed configuration string to the system.

In Phase-I, we developed the supercell methodology, including techniques for analyzing individual cells within the Cell Matrix, handling faulty cells, and configuring new supercells in fault-free regions. We determined how supercells should interact, to cooperatively form a parallel, distributed system which implements the target circuit in the presence of faults. We then designed each of the systems inside a supercell. These designs were then translated to a cell-level specification, resulting in a Cell Matrix configuration string. That string was then used to configure a simulated Cell Matrix, resulting in implementation of the proposed approach. We allowed faulty regions to be introduced into the matrix, and successfully demonstrated the fault handling features of the system.

All Phase-I objectives were satisfied: all systems worked perfectly. For all test circuits, the simulations confirmed that the supercells correctly implemented them. By changing the locations of faults within the matrix, the system was seen to re-implement the target circuit by routing around the faulty regions. Moreover, the parallel operation of the system was verified, i.e., multiple supercells tested and configured multiple regions simultaneously. Thus, system throughput (number of cells being operated on at a given time) actually increased as the supercell count grew. This is an extremely important feature for future reconfigurable systems with extremely high gate counts, e.g., nano-scale devices.

We believe these results justify Phase-II continuation. Phase-I has demonstrated the feasibility and innovativeness of the Cell Matrix for implementing self-repairing circuits, as well as the versatility of the Cell Matrix itself.

Company Name: Cell Matrix Corporation Principal Investigator: Lisa J. K. Durbeck Authorized Contact Person: Lisa J. K. Durbeck Authorized Contact Email: ld@cellmatrix.com

COTR: COTR Email:

Form Printed on 08-15-01 05:10

# Autonomously Self-Repairing Circuits Cell Matrix Corporation 15 August 2001

Submitted as the Final Technical Report for NASA SBIR Phase-I Contract #NAS2-01049

SBIR Rights Notice (Mar 1994)

These SBIR data are furnished with SBIR rights under Contract No. NAS2-01049. For a period of 4 years after acceptance of all items to be delivered under this contract, the Government agrees to use these data for Government purposes only, and they shall not be disclosed outside the Government (including disclosure for procurement purposes) during such period without permission of the Contractor, except that, subject to the foregoing use and disclosure prohibitions, such data may be disclosed for use by support Contractors. After the aforesaid 4-year period the Government has a royalty-free license to use, and to authorize others to use on its behalf, these data for Government purposes, but is relieved of all disclosure prohibitions and assumes no liability for unauthorized use of these data by third parties. This Notice shall be affixed to any reproductions of these data, in whole or in part.

## **Table Of Contents**

| Table Of Contents                                   | 1   |

|-----------------------------------------------------|-----|

| Abstract                                            |     |

| 1. Introduction                                     | 2   |

| 2. Background                                       |     |

| 2.1 Cell Behavior                                   | 3   |

| 2.2 D-Mode Behavior                                 | 3   |

| 2.3 C-Mode Behavior                                 |     |

| 3. Approach                                         |     |

| 3.1 Circuit Configuration in the Presence of Faults |     |

| 3.2 Circuit Configuration Using a Cell Matrix       |     |

| 3.3 Supercell Approach to Circuit Configuration     |     |

| 3.4 Supercell Functional Behavior                   |     |

| 3.4.1 Fault Detection                               |     |

| 3.4.2 Parallel Operation of Supercells              |     |

| 3.4.3 Loop Avoidance-The Link/Lock Network          |     |

| 3.4.4 Parallel Configuration of Supercells          |     |

| 3.4.5 The Supercell's Functional Block              |     |

| 3.4.6 Circuit Genome                                |     |

| 3.4.7 Static ID Assignment                          |     |

| 3.4.8 Dynamic ID Assignment                         |     |

| 3.4.9 Traceback Generation and Parsing              |     |

| 3.4.10 Path Synthesis and the Steering Block        |     |

| 4. Implementation                                   |     |

| 4.1 Supercell Usage                                 |     |

| 4.1.1 I/O Locations                                 |     |

| 4.1.2 Supercell Circuit Synthesis Procedure         |     |

| 4.2 Configuration String Generation                 |     |

| 4.3 Supercell Internals                             |     |

| 4.3.1 Guard Walls                                   |     |

| 4.3.1.1 Semi-Permeable Guard Cells                  |     |

| 4.3.2 Serial Data Formats                           |     |

| 4.3.2.1 Special Bit Streams                         |     |

| 4.3.3 Genome Packing                                |     |

| 4.3.4 Traceback Packing                             |     |

| 4.3.5 Path Synthesis Details                        |     |

| 4.3.6 Delivery of Functional Block Output           |     |

| 4.3.7 Channel Switching                             |     |

| 5. Results                                          |     |

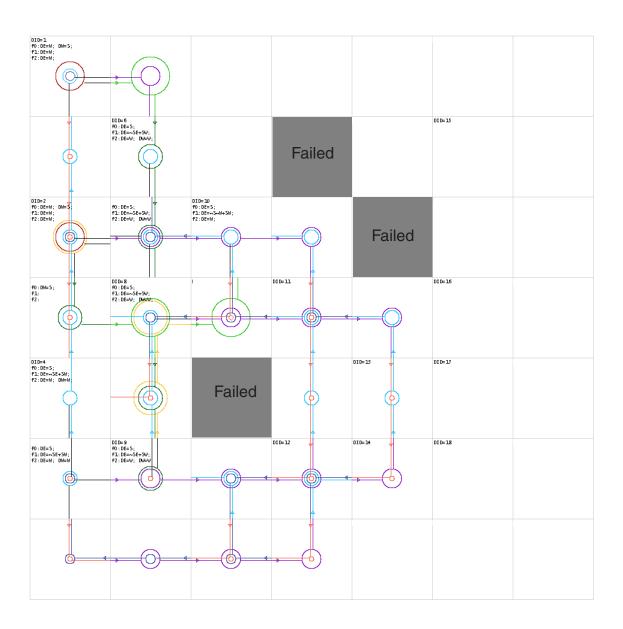

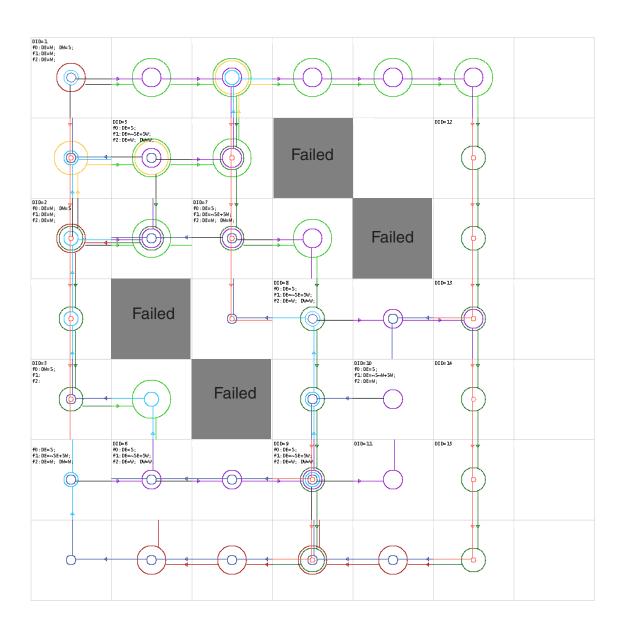

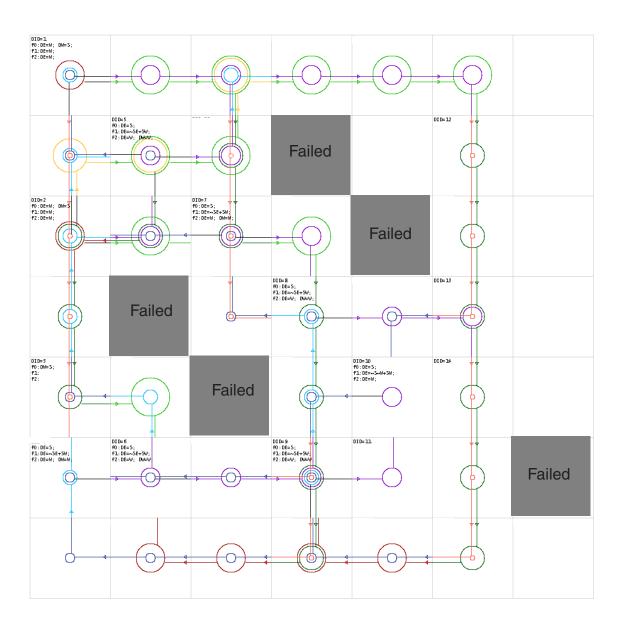

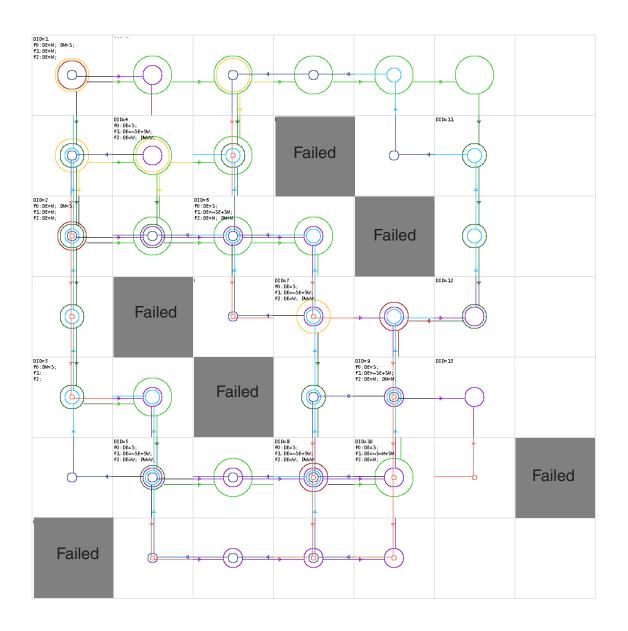

| 5.1 Fault Testing and Parallel Configuration        |     |

| 5.2 Circuit Synthesis Tests                         |     |

| 6. Conclusions                                      |     |

| 7. Acknowledgements                                 |     |

| References                                          | 110 |

### **Abstract**

A self-repairing system based on a novel self-configurable architecture is described. The self-repairing system implements a desired target circuit on a virtual intermediate layer composed of "supercells." These supercells are able to perform all the tasks necessary to implement a target circuit on imperfect hardware, including analysis of the hardware for faults, isolation of faults, synthesis of supercells while avoiding faults, and differentiation of the supercell layer into the target circuit. Moreover, all these operations occur in response to a fixed configuration string that specifies the target circuit. For a given target circuit, the same string is always used, regardless of the location or nature of faults in the hardware. Thus, self-repair is achieved without external fault analysis or configuration string recompilation. This allows the system to autonomously self-repair in response to a single "repair" command.

#### 1. Introduction

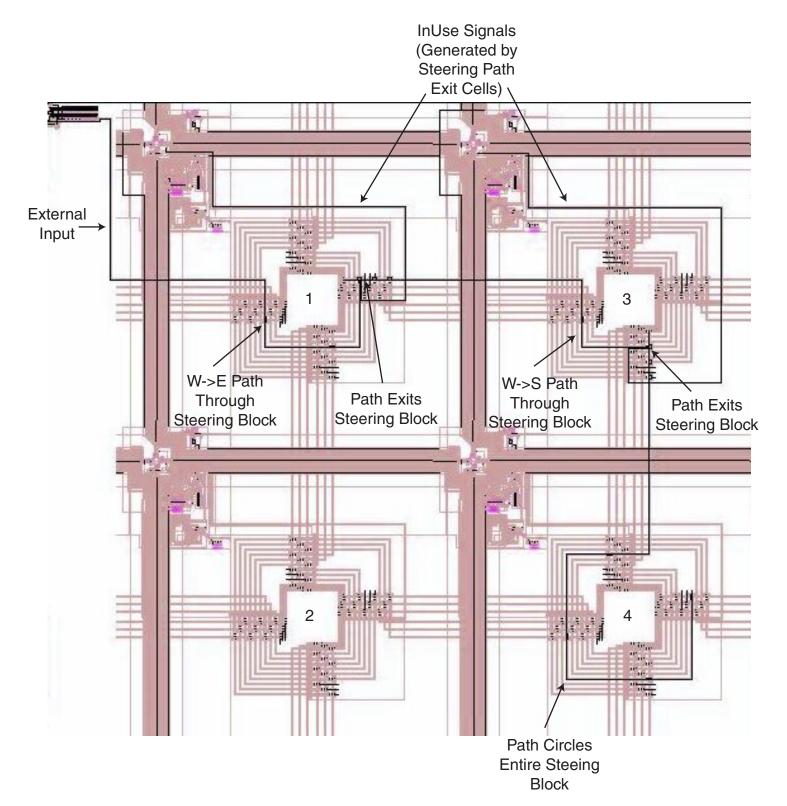

In Phase I of this project, we have designed a system for implementing self-repairing circuits, using a novel reconfigurable platform called the Cell Matrix<sup>TM</sup>. The system, which is implemented **entirely** on a Cell Matrix (i.e., there is no external controller), is able to autonomously reconfigure itself (*self-configure*) to implement a desired target circuit. In the event of a hardware failure, the system can be given a single "repair" command, to which it responds by again reconfiguring itself, thereby re-implementing the target circuit. This self-configuration includes performing an analysis on the Cell Matrix hardware, to determine which regions of the hardware are functioning correctly and which have faults in them. The results of this analysis are used to control the placement and routing of the target circuit within the Cell Matrix. In general, as the location of faults changes, each re-implementation of the target circuit may differ from the previous, based on the new faults. However, the configuration string which is sent to the system is, for a given target circuit, always the same.

Note that this system is completely distributed. There is no centralized processing, nor are there critical elements or irreplaceable components. Most any fault pattern can be handled by the system, provided enough Cell Matrix hardware is available. Excepting the memory which holds and delivers the configuration string, the entire system—including the fault analysis and isolation circuits and the dynamic circuit synthesis—is implemented on the Cell Matrix. All components are themselves subject to the system's fault management, thereby making the system extremely robust.

This robustness is achieved by organizing the Cell Matrix as a collection of *supercells*. Each supercell contains an identical coded description (called a *genome*) of the desired target circuit. The supercells perform 3 major tasks:

- 1. analysis of the Cell Matrix hardware for faults, followed by the building of *guard walls* around faulty regions of the Cell Matrix;

- 2. configuration of non-faulty regions of the Cell Matrix to implement new supercells; and, once a collection of supercells has been implemented,

- 3. implementation of the desired target circuit on top of the supercell collection.

In order for the system to operate autonomously, i.e., without intervention, the same configuration string must be usable in all situations, regardless of the location and number of faults in the hardware. In other words, a single configuration string must be developed for a particular target circuit, independent of any hardware faults which may exist in the Cell Matrix platform. This imposes the minimal requirements for fault-free components, i.e., there must be a memory for storing the configuration string, and a mechanism for feeding this string to certain cells along an edge of the Cell Matrix. As long as those components work, the rest of the system can handle faults inside the Cell Matrix.

Section 2 will present background information on the Cell Matrix architecture. Section 3 describes the details of the supercell approach to self-repairing circuit implementation. Section 4 provides the details of the Cell Matrix implementation of a supercell, including details of how the supercell is used. Section 5 describes the results of a number of experiments, and Section 6 summarizes the results of this project.

## 2. Background

This work is based on a custom reconfigurable system called a Cell Matrix. A Cell Matrix is a hardware system composed of a number of reconfigurable elements (cells) connected in a regular fashion. It is similar to a Field-Programmable Gate Array (FPGA), but differs significantly in the following ways:

- The Cell Matrix is extremely fine grained. Individual cells implement small scale functions, such as simple logic or one-bit addition. Connections between cells are created by configuring cells to act as wires. This provides complete control over the configuration of circuits implemented on the hardware.

- The Cell Matrix is an infinitely-scalable architecture. All connections take place only between immediate neighbors, according to a pre-defined, system-wide topology. This has tremendous implications for future manufacturing technologies such as nanotechnology (Dur 2001).

- The Cell Matrix is *self-configurable*. Any cell within the system has the ability to read and write the configuration information in any of its neighboring cells. This means that configuration operations can be based on analysis of local information, including both pure data as well as cell configuration information. It also means that multiple cells can be configured in parallel, since there is no single external controller, nor is there a single, fixed-size communication channel through which configuration information must be sent.

The Cell Matrix is an inherently fault-resistant architecture, owing to very limited signal exchange among the reconfigurable elements. Despite this limited connectivity, the architecture is rich in its flexibility, and can be used to implement any standard digital circuit. Moreover, because the reconfigurable elements of the Cell Matrix are able to read and write other elements' configuration information, the system supports **self-organizing**, **self-configuring** circuits. This is a feature lacking in almost all other reconfigurable devices currently available. By using self-configurability, it is possible to implement dynamic circuits which change **autonomously** over time. One application of such circuits is to design systems which can reconfigure themselves after new faults have occurred in the hardware. Such systems are then said to be *self-repairing*.

#### 2.1 Cell Behavior

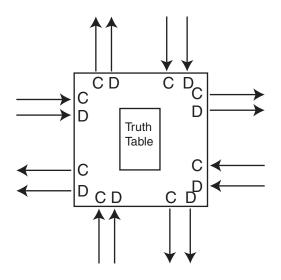

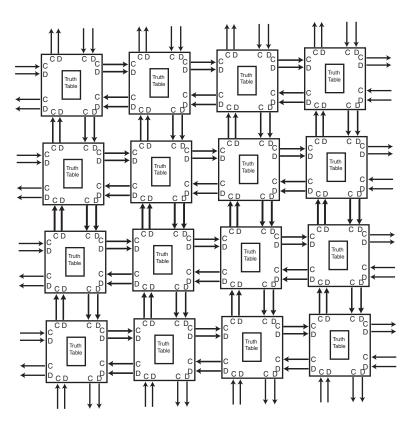

The atomic unit of a Cell Matrix is called a cell. All cells within a Cell Matrix are identical to each other. Figure 2.1 shows an example of a single Cell Matrix cell. Such cells are connected to other cells using a fixed connection scheme, so that outputs from a cell are continuously provided to the inputs of neighboring cells, based on a fixed, system-wide topology, as shown in Figure 2.2. By properly configuring cells in such an interconnected set, digital circuits can be implemented.

Throughout this work, we concentrate only on four-sided cells, arranged in a two-dimensional array so that each cell has four adjacent neighbors<sup>1</sup>. Each cell has two inputs, labeled C and D, and two outputs (also labeled C and D) on each of its sides.

Each cell operates at any given moment in one of two modes: D-mode and C-mode. One cell's mode is effectively independent of the mode of other cells around it. It's mode is determined entirely by its C inputs. If any C inputs to a cell are 1, the cell is in C-mode; otherwise it is in D-mode.

## 2.2 D-Mode Behavior

In their simplest mode (called "D-Mode"), cells act as pure combinatorial processing elements. Cells accept inputs from neighboring cells, process them based on a per-cell *configuration memory* or *truth table*, and produce outputs accordingly.

<sup>&</sup>lt;sup>1</sup> Note that cells on the edge of the entire matrix have only three neighbors, while cells in corners have only two neighbors. Such edge cases are important, as the unconnected sides can be made available to external connections, thereby allowing external control and analysis of the Cell Matrix.

Figure 2.1

Basic Cell Matrx Cell Layout

Data enters and exits through the D lines

Cell's Mode is onctrolled by the C inputs

C outputs affect neighboring cells' modes.

Figure 2.2 4x4 Collection of Cell Matrix Cells

Cells are typically configured to perform small-scale operations such as 2-, 3- or 4-input logical operations, multiplexing, one-bit addition, and so on. Cells are also used to implement wires, which pass data from a cell on one side to a cell on another, thereby allowing non-adjacent cells to exchange information. Collections of cells can be used to implement larger circuits, such as arithmetic units, complex logic, and so on. Collections of cells can also be used to implement sequential circuits, such as flip flops, memories, counters, and state machines. Therefore, a Cell Matrix can be used to implement traditional digital circuits, following standard digital circuit design methodologies.

#### 2.3 C-Mode Behavior

The more unique aspects of a Cell Matrix arise when cells are operating in C-mode. A cell is placed in C-mode when any of its C inputs are 1. Assuming only one of a cell's C inputs is asserted, we may call the side where Cin=1 the "active side." A C-mode cell's behavior can then be described as follows:

- 1. the "last" bit (based on some pre-defined ordering) of the cell's configuration memory is presented to the D output of the active side;

- 2. on the rising edge of a system-wide clock, the D input on the active side is sampled; and

- 3. on the falling edge of the system-wide clock:

- the sampled D input is shifted into the beginning of the C-mode cell's configuration memory;

- the entire configuration memory is shifted by one bit; and

- the last bit of the configuration memory (which was formerly presented on the active side's D output) is lost..

This sequence of steps means that if cell X places cell Y into C-mode, cell X can read and write cell Y's configuration memory, via X's D inputs and outputs.

Since a cell's configuration memory completely defines the cell's D-mode behavior, the above mechanism allows a cell to analyze and modify the behavior of neighboring cells. Using the C-mode of cells, circuits can be built which process *circuit configuration information* in the same way that other circuits process numeric or logical data. As a result, circuits can be built which synthesize other circuits, which self-replicate, or which otherwise dynamically modify themselves.

Further details of the Cell Matrix can be found in the original Cell Matrix architecture patent (Mac1 1999), as well as (Mac3 1999) and the Company's Website (CMC).

## 3. Approach

Implementing a digital circuit on a reconfigurable platform P is normally a straightforward process. The circuit can be viewed as a graph, whose nodes are primitive elements (such as AND gates, flip flops, etc.), and whose edges represent connections among those elements. This graph is translated to a configuration string (a process normally called *place and route*), which, when sent to P, configures P's elements and interconnections so as to implement the desired circuit.

#### 3.1 Circuit Configuration in the Presence of Faults

The process is more complicated if the hardware contains faults, such as elements which do not function properly, or interconnections which do not transmit data properly. If the locations of such faults can be determined, as well as the locations of any other elements or connections which do not behave properly because of those faults, then the place and route process can simply avoid those locations, treating them as unavailable resources.

Things are not as easy if the place and route process is not on-board the remote system. For example, if a system on a satellite has failed, it may not be practical to analyze the hardware from a ground station, re-run the place and route, and upload a new configuration string. Rather, it may be desirable to send a simple "repair" command and have the system reconfigure itself. This would permit the use of a single configuration string to configure the system at any time, regardless of where the faults may exist. The system would then only require a memory to store the configuration string, and a mechanism for delivering that string to the reconfigurable platform.

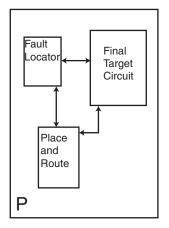

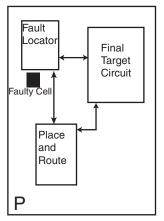

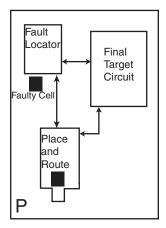

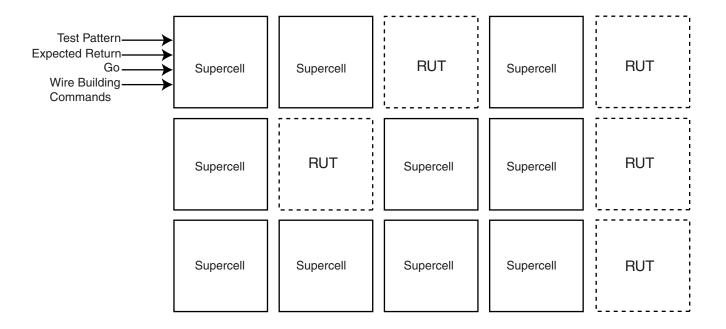

Note that adding an external fault locating system and a place and route processor is not an ideal solution, since these additional pieces are themselves subject to possible failures. Therefore, it is desirable that the reconfigurable system should not only implement the desired target circuit, but also whatever circuitry is necessary for determining *how* to implement the desired circuit. Figure 3.1a illustrates this situation. On reconfigurable platform P, there is not only the desired target circuit, but also the fault locator and the place and route algorithm. The location and exact

configuration of each of these elements may change, depending on the presence of faults within P, as shown in Figures 3.1b and 3.1c.

## 3.2 Circuit Configuration Using a Cell Matrix

The Cell Matrix possesses a natural self-duality which makes this type of system implementation possible. It is, in fact, exactly these types of self-referential systems for which the Cell Matrix was designed.

To implement a perfectly functioning circuit on a faulty hardware platform, four things must be done:

- 1. faulty regions of the hardware must be detected;

- 2. these faulty regions must somehow be isolated from other regions of the hardware, to prevent their malfunction from spreading;

- 3. the elements of the desired circuit must be implemented using only the good areas of the hardware; and

- 4. these elements must be interconnected, again using only the good areas of the hardware.

Moreover, each of these steps should be performed by the system itself, without any external control, other than the supplying of a fixed configuration string.

#### 3.3 Supercell Approach to Circuit Configuration

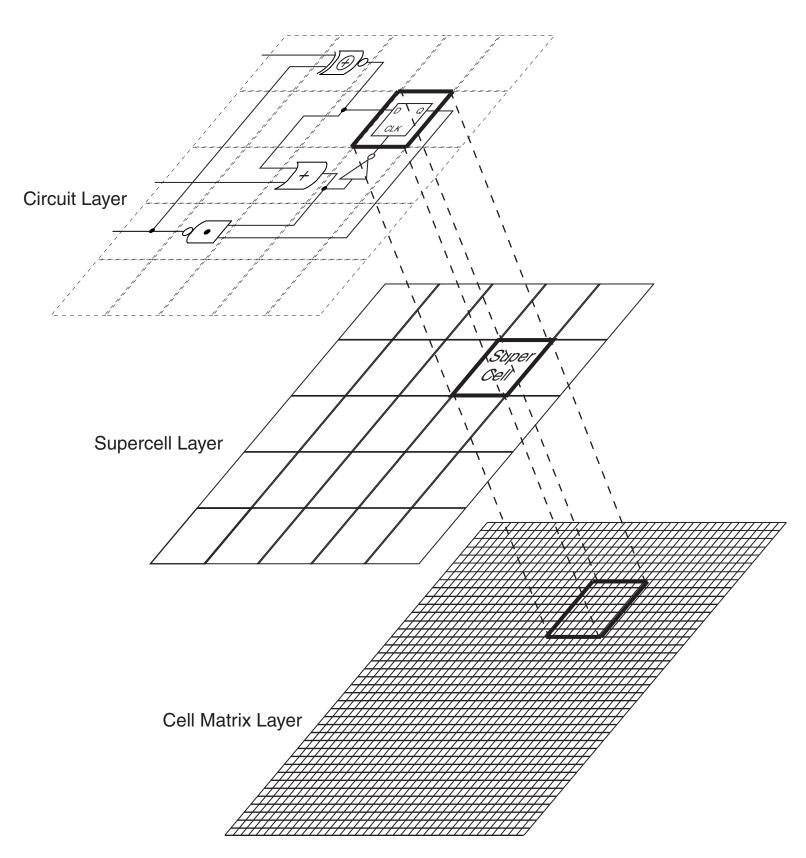

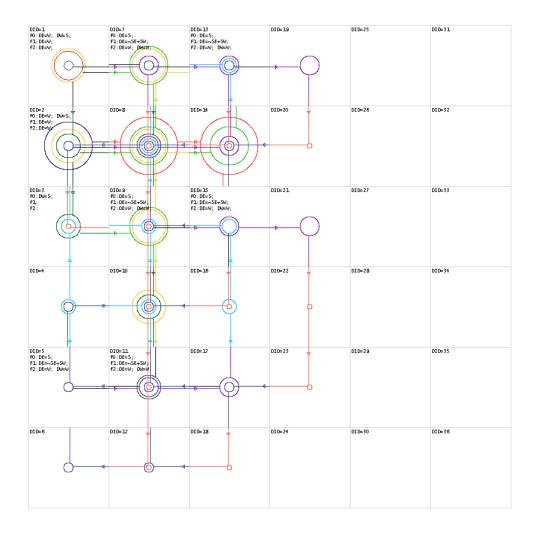

In order to achieve these goals, we have implemented what is effectively an intermediate layer between the Cell Matrix hardware and the desired target circuit. This layer, called the *Supercell Layer*, is responsible for analyzing the underlying hardware, detecting and isolating faults, and then implementing the target circuit on top of itself. It is composed of higher-order cells called *supercells*, themselves composed of Cell Matrix cells. Figure 3.2 illustrates this conceptual organization. Note that the hierarchical view in Figure 3.2 is an organizational hierarchy, not a physical one. The supercell layer and target circuit layer do **not** consist of physically distinct hardware. The entire system is a single Cell Matrix, composed of perfectly identical cells.

#### 3.4 Supercell Functional Behavior

The supercells perform all necessary functions for fault-free implementation of the target circuit. These functions will be described below in the following sections:

- 3.4.1 Fault Detection

- 3.4.2 Parallel Operation of Supercells

- 3.4.3 Loop Avoidance-The Link/Lock Network

- 3.4.4 Parallel Configuration of Supercells

- 3.4.5 The Supercell's Functional Block

- 3.4.6 Circuit Genome

- 3.4.7 Static ID Assignment

- 3.4.8 Dynamic ID Assignment

- 3.4.9 Traceback Generation and Parsing

- 3.4.10 Path Synthesis and the Steering Block

#### 3.4.1 Fault Detection

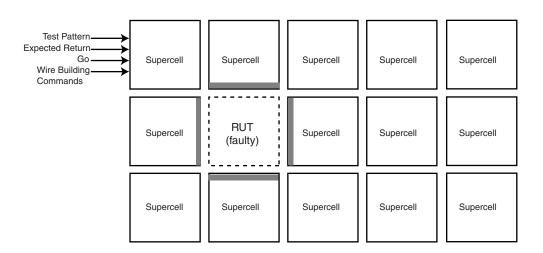

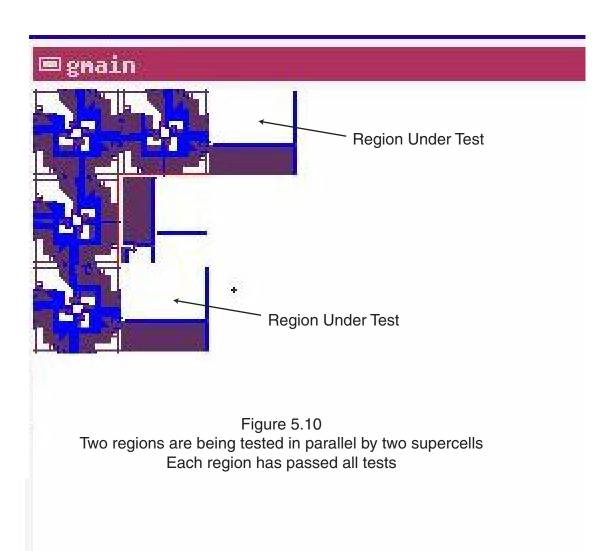

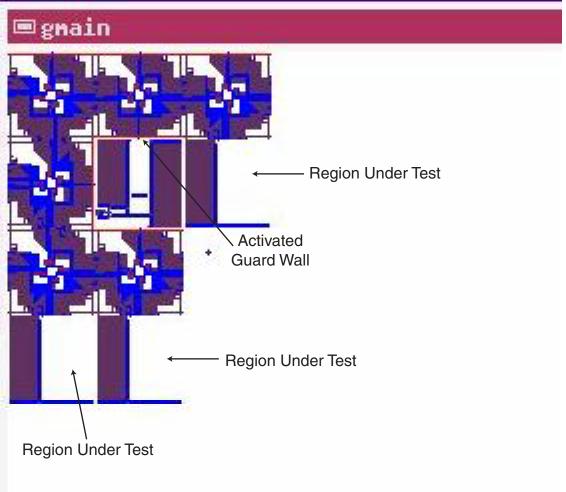

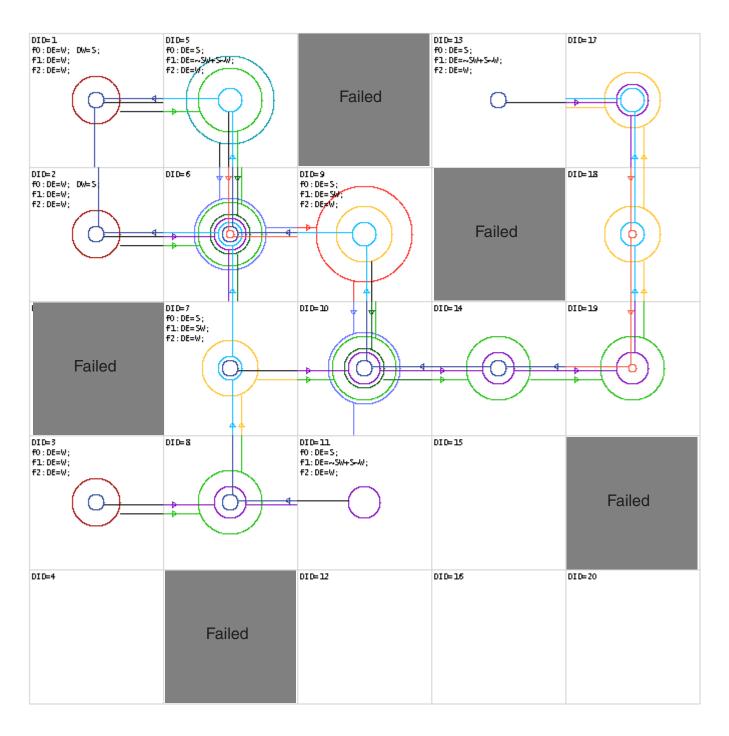

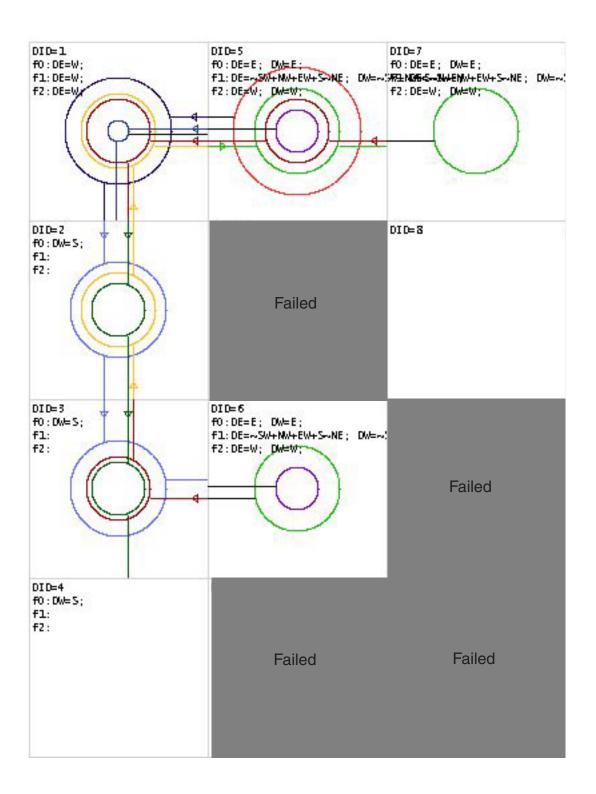

The first task of a supercell is to locate faults within the hardware. This is done by testing each cell inside the Cell Matrix, via a series of tests which exercise the cell's basic functions (configurability, processing of inputs, delivery of outputs). Multiple regions, each the size of a supercell, are tested in parallel, so that they may be subsequently configured to act as new supercells.

Figure 3.1(a)

Possible Implementation

of Self-Repairing

Circuit

Figure 3.1(b)

Same System with

a Single Faulty Cell.

Fault Locator has

moved up.

Figure 3.1(c)

Same System with

Multiple Faults.

Place and Route

block has been

reshaped.

Figure 3.2 Hierarchical View of Supercell-Based Circuit Layout

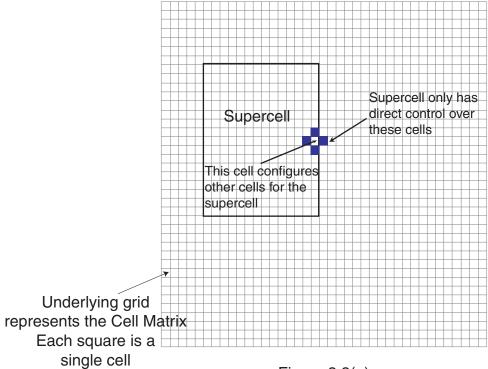

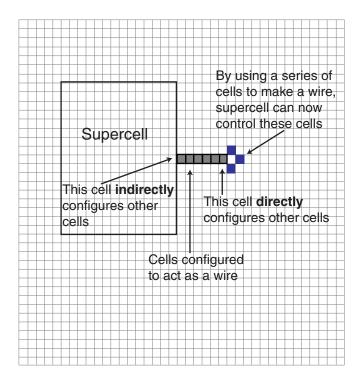

Since a supercell is implemented on a Cell Matrix, the cells of the supercell have the ability to read and write neighboring cells' configuration information. Note however that direct control is only available over cells that it is physically connected to, i.e., the immediately adjacent ones. However, by carefully orchestrating the configuration of adjacent cells, they can be caused to convey configuration information to their immediate neighbors, and so on, as shown in the progression from Figure 3.3(a) to Figure 3.3(b). Such configurations of cells are called wires<sup>2</sup>, and they are used extensively to allow a supercell to gain access to non-adjacent cells.

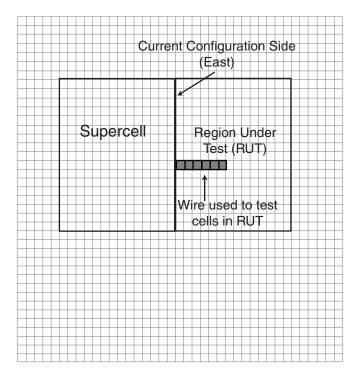

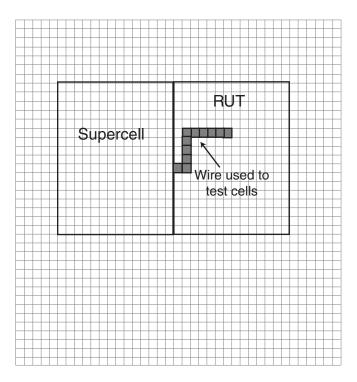

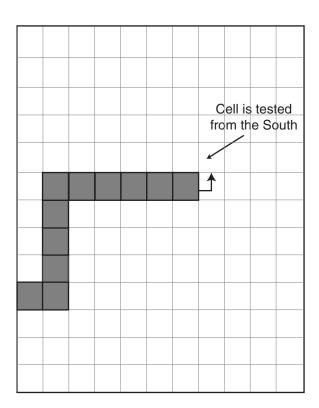

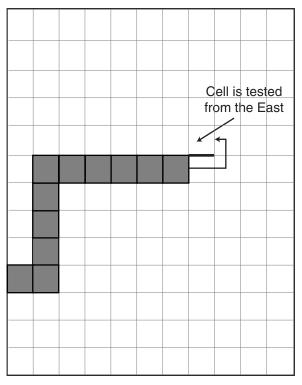

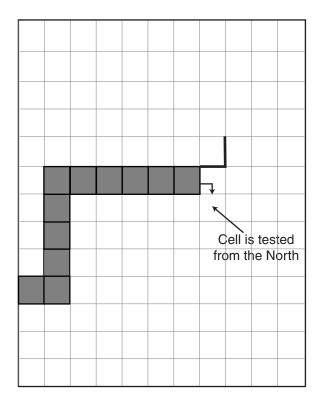

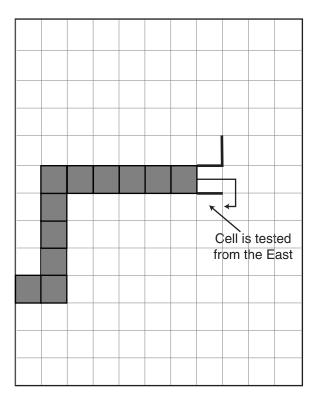

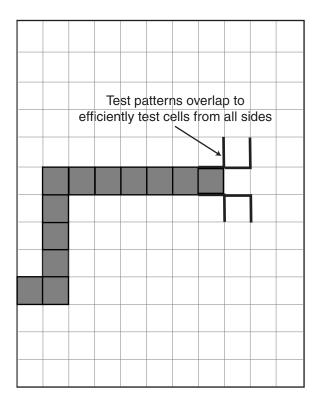

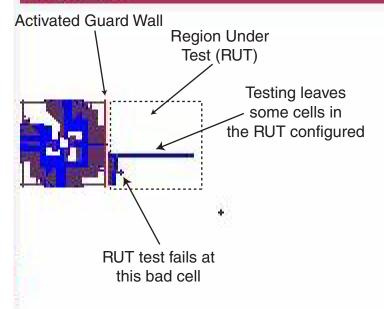

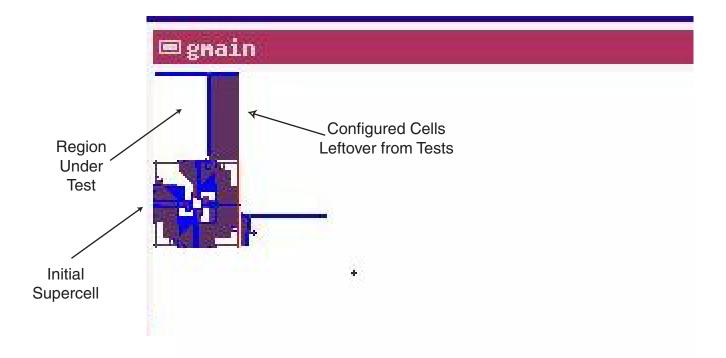

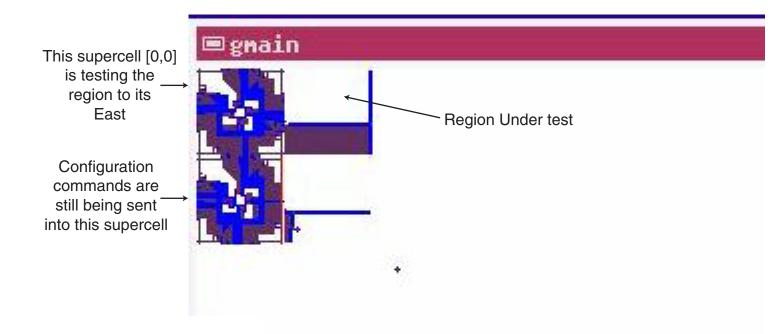

At any given time, fault detection is performed to only one side of a supercell, called the *current configuration side*. In Figure 3.4, the supercell is testing cells to its East. Within this region under test (RUT), wires are built to allow access to each cell. Cells within the RUT are accessed from all four sides (3 sides for cells along an edge, two sides for cells in a corner). Figures 3.5a-3.5f show how this multi-side access is achieved. Note that for each configuration of the test wire, two cells are being tested, each from two sides. Following this, the wire is extended one cell to the East, and the four tests are repeated (Figure 3.5f). At the end of the row, the wire is moved down on row, and the sequence repeats. This test ordering ensures that all cells within the RUT are tested from all internal side, while minimizing the total number of configuration operations needed to test all cells within the RUT.

Once all cells within a column of the RUT have been tested, the wire is rebuilt so that cells in the next column to the left will be tested, and so on. Special sequences are used for the edge cases.

From each side, the cell under test (CUT) is tested with the following two tests<sup>3</sup>:

- 1. the cell is configured as an inverter, and a test pattern of alternating 1s and 0s is sent to the cell. This tests the ability of the cell to implement a non-zero function, thus detecting faults in the configuration logic. It also forces the inputs and outputs to respond to and generate both 1s and 0s, thereby detecting stuck-at faults in the cell's D inputs and outputs.

- 2. the cell's configuration memory is loaded with an irregular test pattern, which is then read out of the cell's configuration memory. This tests the configuration memory's ability to store a given test pattern. Since the configuration memory is implemented as a shift register, this detects stuck-at faults in the memory itself, as well as any faults in the control logic responsible for shifting the memory, detecting the mode changes of the cell, and so on.

To perform each test, a GO signal is sent to the supercell, along with a test pattern and an expected return pattern. The GO signal indicates that the test pattern should be sent along the wire to the CUT. The output X of the CUT is transmitted back through the wire, and compared to the expected return pattern Y. Any difference between X and Y indicates a failure in the RUT, possibly in the CUT, or possibly in some other cell used to build the wire. Regardless of the cause, if  $X \neq Y$ , it indicates a problem in the behavior of some cell or cells within the RUT, and the RUT is deemed unusable. Note that because supercells are only placed in regions which have already been determined to be fault-free, test failures can be taken to indicate failures in the region under test, as opposed to failures in the circuit performing the test.

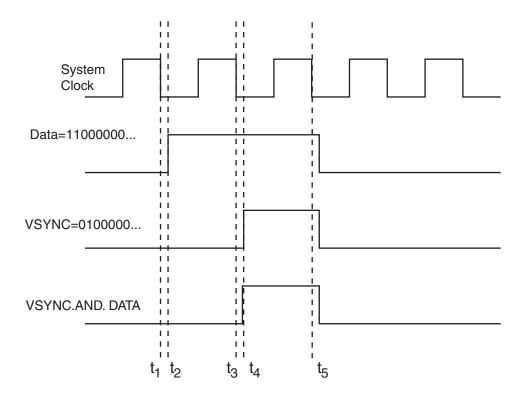

It is important to manage timing issues in comparing X and Y, since Y is a stored pattern, and is thus available before X, which is a generated pattern. The timing is synchronized to the system-wide clock, and comparisons are only made on the rising edge of that clock, while the patterns X and Y change on the falling edge.

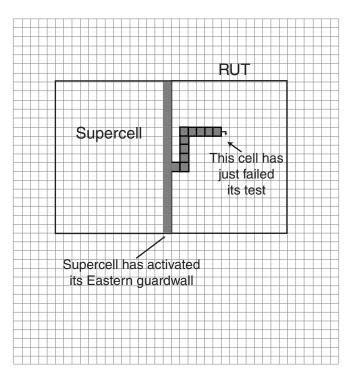

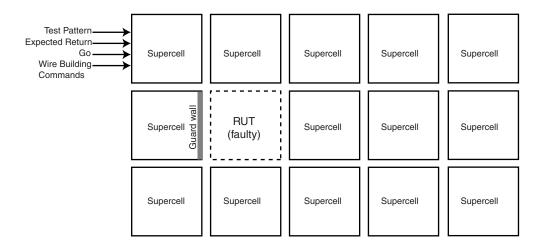

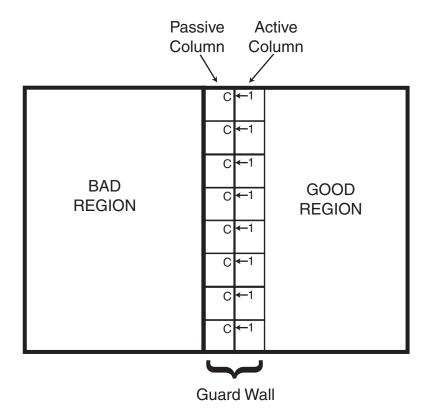

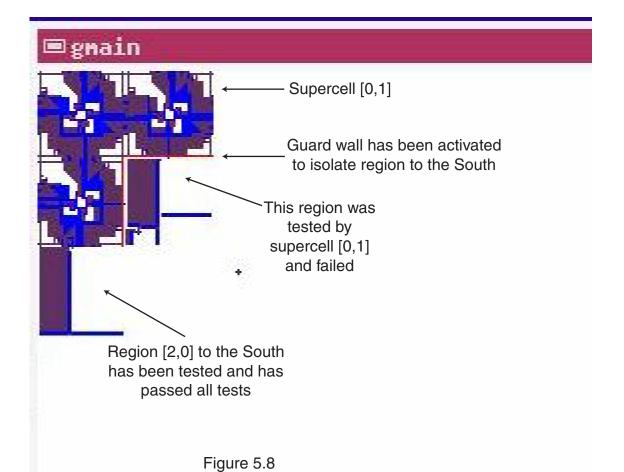

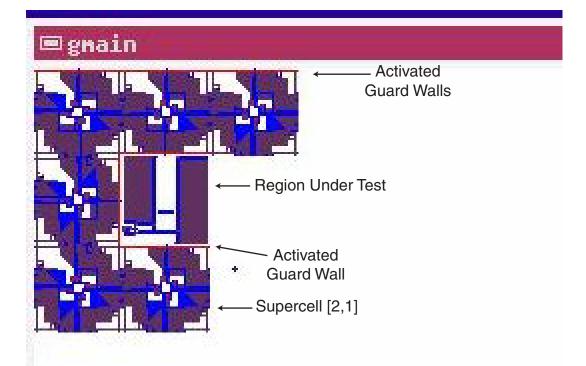

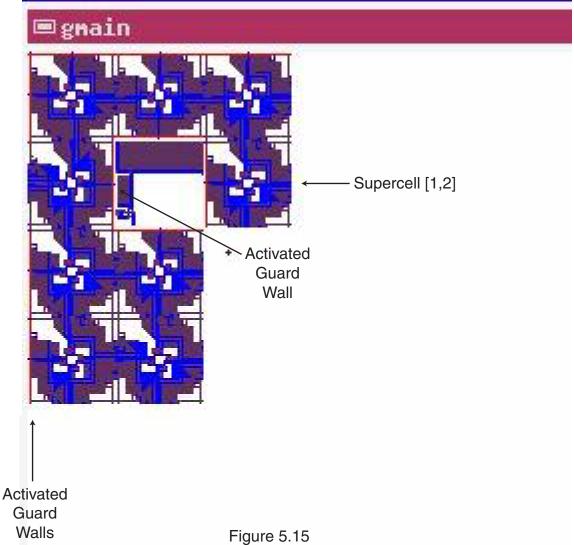

Once a fault is detected, the supercell activates a guard wall along the side from which it is testing the RUT. This guard wall, which will be further explained in section 4, makes it impossible for any cell in the RUT to affect any cell inside the supercell. Note that the guard wall is actually part of the supercell itself, and therefore can be assumed to be composed of non-faulty cells. Figure 3.6 shows a supercell which has activated one of its guard walls following a test failure. Eventually, other supercells (on other sides of the RUT) will also detect the fault, and

<sup>3</sup> Note that it is easy to add other tests and test patterns as well. For example, if hardware analysis revealed that a

of 0000000111111111... could be used.

common failure mode was the shorting together of bits 8 locations apart in the configuration memory, a test pattern

<sup>&</sup>lt;sup>2</sup> These configurations are disclosed in US Patent Application #09/702,574, filed 31 Oct 2000.

Figure 3.3(a)

Supercell's direct control is normally limited

Figure 3.3(b) 6-Cell Wire used to control non-adjacent cells

Figure 3.4

Supercell builds wires to test cells in the Region Under Test

Figure 3.5(a)

Supercell has built a wire into the RUT

Figure 3.5(b)

One cell is being tested from the South

The supercell and part of the RUT are not

displayed in this figure

Figure 3.5(c)

Same cell is now being tested from the East

The dark line indicates tests which have already been performed

Figure 3.5(d)

A different cell is now tested from the North

Figure 3.5(e)

Same cell is now tested from the East

Figure 3.5(f)

Wire has been extended one cell to the East and all four tests have been repeated

Figure 3.6 Supercell has detected a faulty cell in the RUT and has responded by activating one of its guardwalls

activate their own guard walls. In this way, a collection of supercells will form a continuous ring of guard walls around the entire faulty area.

## **3.4.2** Parallel Operation of Supercells

The above description describes the behavior of a single supercells testing a single RUT. However, in a typical setup, there will be many supercells, all operating in parallel, each testing its own RUT. Figure 3.7 shows a typical situation. Again assuming regions to the East are being tested, there are five RUTs in this figure. Note that the test pattern, expected return pattern, GO command and wire-building commands are being sent to only one supercell (the upper left in this example). Each supercell which receives these inputs transmits them to *each* of its four sides in one of three ways:

- If the supercell's side is adjacent to another supercell, it transmits them as simple data. The receiving supercell accepts them as data, and transmits them according to these same rules.

- If the supercell's side is **not** adjacent to another supercell, and that side has been designated as the current configuration side (East in this example), then they are treated as live commands: the wirebuilding commands are used to configure cells to create wires, and if the GO command is asserted, the test pattern is sent through the wire, with the return pattern compared to the expected return as described above.

- If the supercell's side is not adjacent to another supercell, and that side has **not** been designated as the current configuration side, then nothing is transmitted through that side.

In this way, test patterns and commands can be sent to a single supercell, transmitted to the perimeter of the entire supercell collection, and new regions can be added in an orderly fashion. Thus, as the collection of supercells grows, so does the number of RUTs being tested simultaneously. **This is one key advantage of the Cell Matrix approach-the ability to perform fault detection on a number of regions in parallel.**

By performing the above tests while changing the current configuration side to each of North, South, West and East, faults end up completely isolated, as shown in Figures 3.8a-3.8d. Since cells are tested from all sides, each supercell which tests the RUT containing the fault will detect the failure, and activate its guard wall on the corresponding side. The result is a closed ring of guard walls, completely isolating the faulty cell from the properly-functioning supercells. Note that this also works for larger faults which span more than one supercell region.

#### 3.4.3 Loop Avoidance-The Link/Lock Network

There is a technical detail to the above description. Since supercells transmit data to all their sides, there is a strong potential for transmission loops to form. If supercell A receives a GO command, and passes it to adjacent supercell B to its East, B would immediately turn around and transmit this back to supercell A. A and B have now formed a loop, and the GO command is trapped inside that loop. If the original transmission to A is terminated, A will still be receiving GO from B, and will continue to retransmit it back to B. Such a state is unrecoverable.

To avoid this loop problem, everything is built on top of a dynamically-built, loop-free network called a *Link/Lock* (*L2*) *Network*. The L2 network is assembled using a handshake between supercells consisting of two signals:

- a LINK output from supercell X to supercell Y means X is on the network, and Y should add itself to the network

- ullet a LOCK output from supercell X means X is already on the network, and therefore no new LINK signals should be sent to X

The L2 network can be initiated from any supercell, which transmits "link" commands to all adjacent supercells which are not already on the network. Any supercell receiving a link command joins the supercell network, and in turn transmits link commands to each of *its* neighboring supercells which is not already on the network. When a supercell joins the network, it begins transmitting "lock" signals to all its sides, indicating that it is already on the network. In this way, a supercell X can tell if an adjacent supercell Y is already on the network by checking Y's lock output. If lock is not asserted, X can assert its LINK output, causing Y to join the network.

Once assembled, signals such as wire building commands can be piggybacked on top of the L2 network's link signals to achieve loop-free broadcasting of signals throughout the connected set of supercells. Note that signals can also be broadcast *from all* supercells back to the originator of the L2 network by transmitting in the reverse direction of the link signals.

Figure 3.7

Set of supercells performing a parallel test

of five Regions (RUTs)

Only one supercell is sent the test-related commands.

That supercell transmits those commands to all other supercells.

Figure 3.8(a)

RUTs which passed the Eastern test are now configured as supercells. One RUT contains a fault, causing the testing supercell to activate its Eastern guard wall (shown in gray).

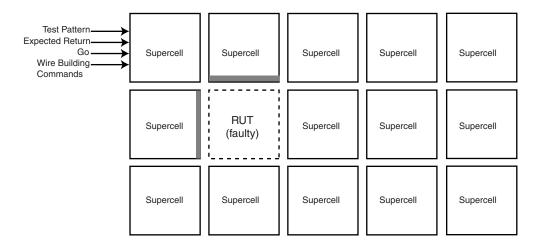

Figure 3.8(b)

Following a Southern test sequence, one supercell has now activated its Southern guard wall.

New RUTs are not shown.

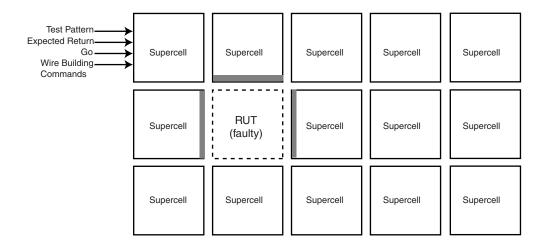

Figure 3.8(c)

Result of Western test sequence

Figure 3.8(d)

Result of Northern test sequence.

Faulty RUT has now been completely isolated by surrounding guard walls.

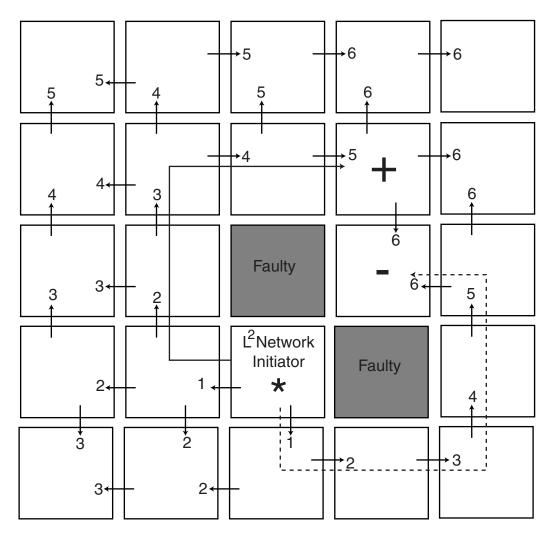

Figure 3.9 shows an example of the building of an L2 network. In this example, the supercell marked "\*" is the initiator of the L2 network. Each arrow represents a link signal; the number next to an arrow shows the step at which the link signal was asserted. By building the L2 network in steps like this, the effect is that shortest paths are constructed, while longer paths are blocked by the LOCK signals. For example, the solid line shows a pathway (via the L2 network) from the initiator "\*" to the supercell marked "+." This pathway is 5 supercells in length. There is another possible pathway, as shown by the dashed line. However, that pathway (which would have a length of 7) terminates in the supercell marked "-." When the L2 construction reaches node "-" (at step 6), node "+" has already joined the L2 network, and is thus asserting a LOCK signal to node "-." This is a direct consequence of the shorter path length of the solid path vs. the dashed path.

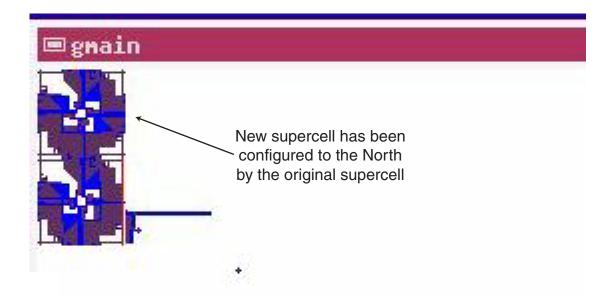

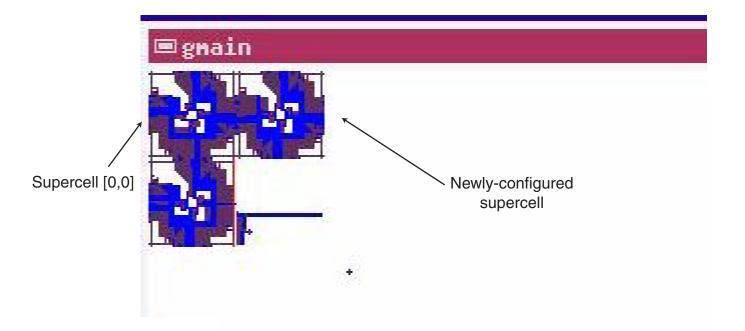

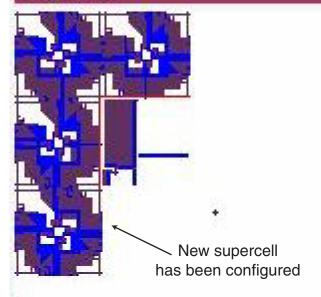

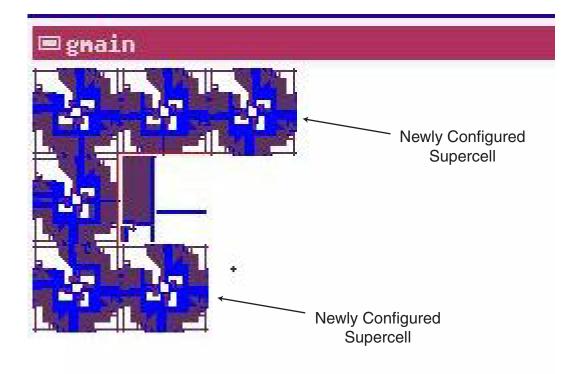

#### 3.4.4 Parallel Configuration of Supercells

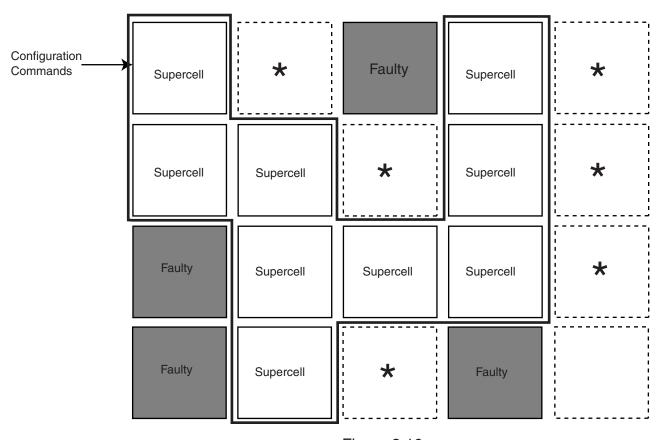

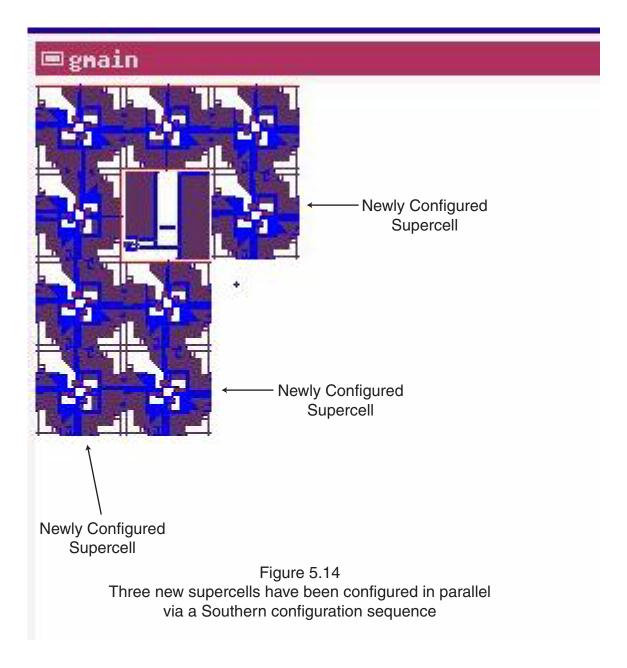

In addition to performing testing of the Cell Matrix in parallel, there is another more basic task which the collection of supercells must perform in parallel, and that is the configuration of new supercells. Using the techniques described above (3.4.1-3.4.3), an existing set of supercells can transmit configuration information to all perimeter supercells in some fixed direction. As is the case with fault testing, at any given time, configuration of new supercells occurs on only one side of the current supercell perimeter. In Figure 3.10, the indicated supercells are transmitting configuration information to the East. Non-perimeter supercells pass this information to adjacent supercells, while perimeter supercells use this information to build new supercells (by configuring Cell Matrix cells near their edge). The cells in regions marked with "\*" are being configured to act as new supercells. As in the case of fault testing, the number of supercells being built in parallel increases as the size of the supercell network increases.

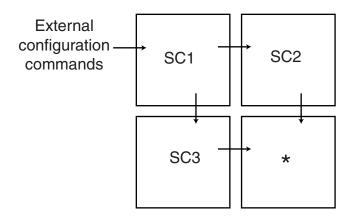

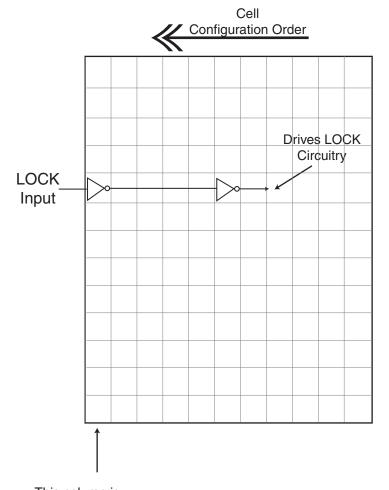

Note that as a new supercell is being constructed, the cells which will make up its edges may already be receiving signals from other adjacent supercells. For example, in Figure 3.11, three supercells have been constructed, and a fourth region ("\*") is being configured as a new supercell. While "\*" is being configured, SC2 and SC3 are sending Link/Lock signals and configuration information to the "\*" region. The supercells have been carefully designed so that, as they are being configured, this always-present incoming information does not cause them to malfunction. Figure 3.12 shows how this is handled (again concentrating on building to the East). The incoming LOCK signal is inverted in the leftmost column of each supercell, and then inverted again inside the supercell. Since the leftmost column of cells is configured last (that's how the supercell configuration mechanism was written), the internal LOCK signal will be a one (inverted 0) until the leftmost column is configured. Because of this, the newly-forming supercell will not join the L2 network until the leftmost column has been built, at which point the internal circuitry for proper Link/Lock arbitration will have already been built. Similar control is applied for building to the North, West and South.

As soon as the configuration of cells within the "\*" region is completed, the new supercell in that region will join the L2 network, and commence relaying and/or executing any commands which are sent to it.

Further details of how the configuration information is generated will be described in Section 4.

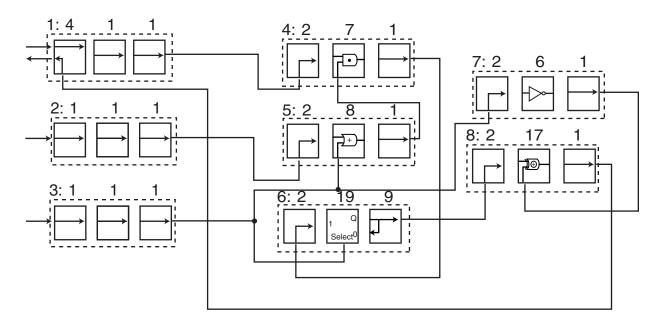

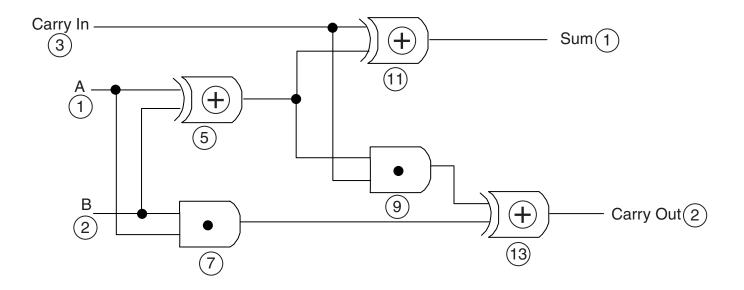

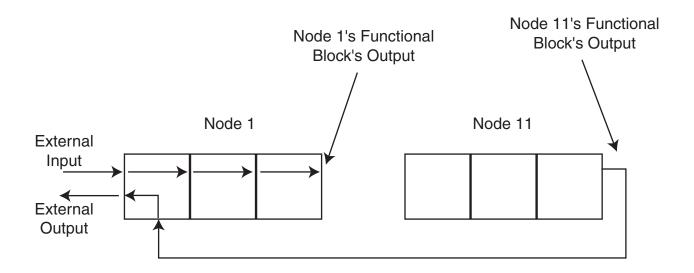

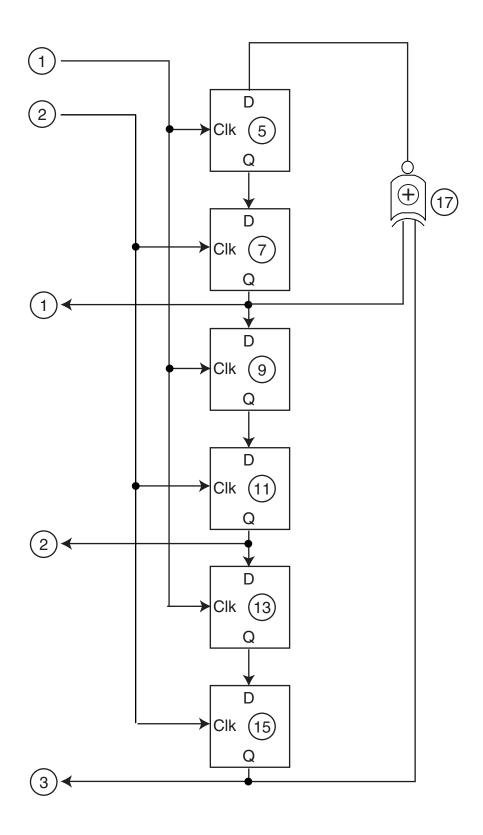

#### 3.4.5 The Supercell's Functional Block

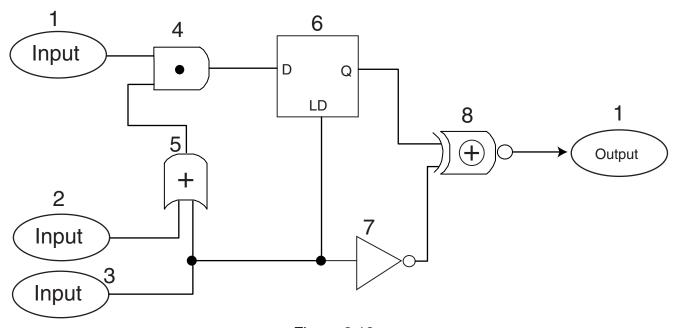

In implementing the final desired circuit on top of the supercell network (as in Figure 3.2), each node of the circuit will be implemented in a single supercell. For example, the circuit in Figure 3.13 contains 5 nodes. Each of these nodes will be implemented in a single supercell.

Accordingly, there must be some way to indicate what function each supercell is to perform in the final circuit. This per-supercell function is called the supercell's *functional block*. The functional block is the piece of the supercell which is incorporated in the final target circuit's implementation.

In this proof-of-concept version of the supercell, we have used an extremely simple functional block, consisting of only three Cell Matrix cells. In a more practical version, the functional block would be much larger, to allow functional units on the scale of state machines, larger memories, digital filters, and so on, instead of only simple gates and small-scale devices. However, regardless of the size of the functional blocks, their implementation and use is consistent with what is described here.

Figure 3.9 Sample Link/Lock Network

Supercell marked "\*" is network initiator. Arrows indicate LINK outputs.

Numbers at the head of an arrow indicates the step at which that LINK output is activated.

Solid line shows resulting path from "\*" to "+". Dashed line shows alternate path,

which is longer, and hence ends in "-"

Figure 3.10

Supercells are configuring new supercells to the East of current perimeter (perimeter is shown by dark line).

Supercell in upper left corner receives external configuration commands. Non-perimeter supercells pass the information to other supercells via the Link/Lock network.

Perimeter supercells configure regions to the East to act as new supercells.

Figure 3.11

"\*" is being configured by SC3 as a new supercell

While being configured, region "\*" is also being sent LINK and other signals from the North by SC2. Supercells must handle receipt of these signals while they are being constructed.

This column is configured last

Figure 3.12

Internal LOCK signal is a twice-inverted copy of the external LOCK input. Prior to configuring the leftmost column, the internal LOCK signal will be 1, and the supercell will not initiate any outgoing LINK requests. When the leftmost column is built, the incoming LOCK signal is correctly passed to the internal LOCK circuitry. This mechanism is repeated on all four sides of the supercell.

Figure 3.13

Sample Final Target Circuit

Node numbers are shown above components.

Each node will be implemented in a supercell.

Node assignments for Inputs an Outputs are not shown.

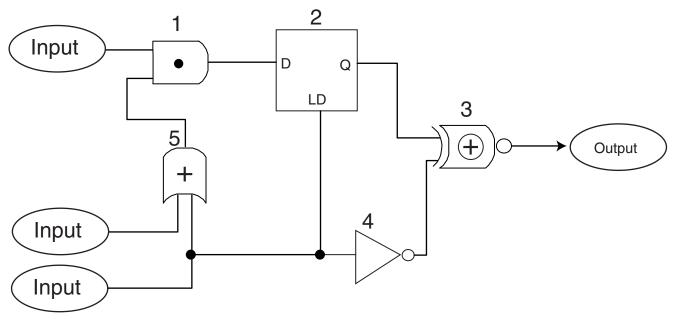

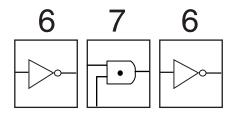

To allow maximum flexibility in the use of the cells making up the functional block, each cell's behavior can be specified independently of the other cells within the block. To avoid having to specify the entire truth table of a cell, one layer of indirection is added. Figure 3.14 shows the mapping table from cell codes to actual cell configurations. For example, to configure a cell within the block to act as an inverter, the code 6 is used, while an AND gate is coded as a 7.

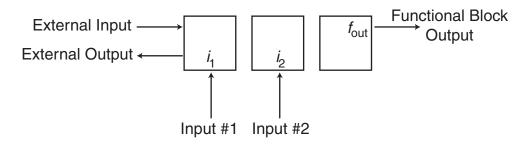

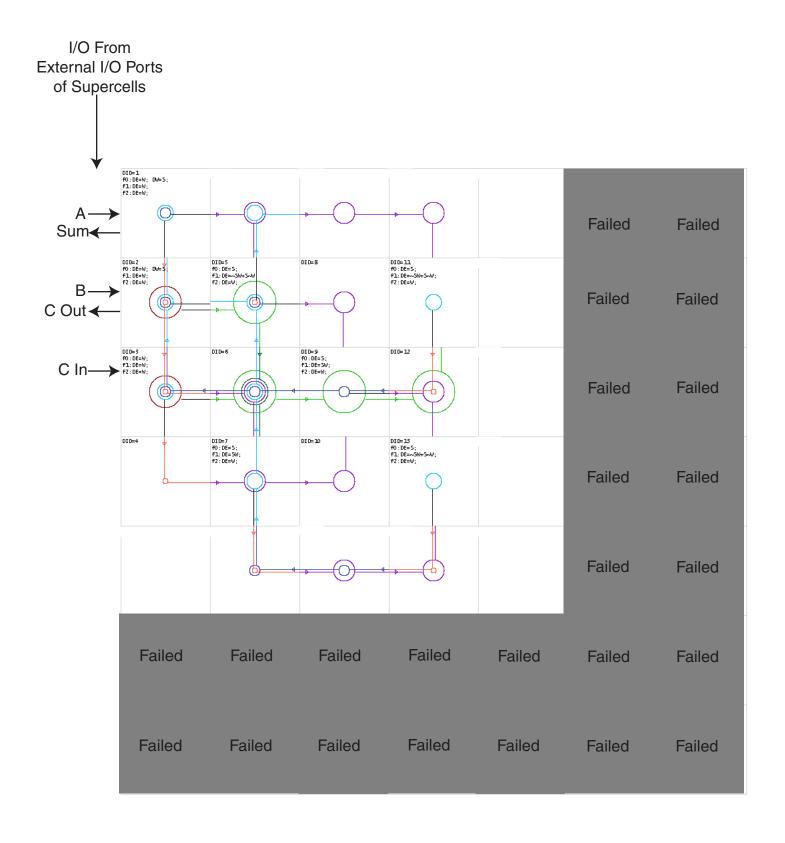

The functional block is shown in Figure 3.15. The three cells making up the block are labeled 1, 2 and 3. The actual output of the functional block is labeled  $f_{out}$ , and is generated by the Eastern output of cell 3. This output can be connected (via the supercell network) to the inputs of other functional blocks. The inputs to the functional block are labeled  $i_1$  and  $i_2$ , and are delivered to the southern inputs of cells 1 and 2 respectively. These inputs can be connected (via the supercell network) to the  $f_{out}$  outputs of other functional blocks. By connecting these inputs and outputs appropriately, the desired target circuit is constructed.

Additionally, there are two special I/O lines connected to the Western edge of cell 1. These are used for transmitting information between the functional block and the outside world. They are directly connected to cells on the western edge of the supercell. Thus, functional blocks on supercells in the western-most column of the supercell network may be accessed from outside the Cell Matrix. This is the mechanism used for writing and reading data to and from the final target circuit.

Each of the three blocks can be configured independently. For example, the functional block in Figure 3.16 reads an external input, inverts it, and ANDs it with input  $i_2$ . The result is inverted in cell 3 and sent as the functional block's output  $f_{\text{out}}$ . Thus this functional block implements a NAND with one inverted input. The block is specified by the ordered triple 6, 7, 6.

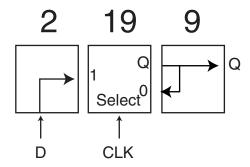

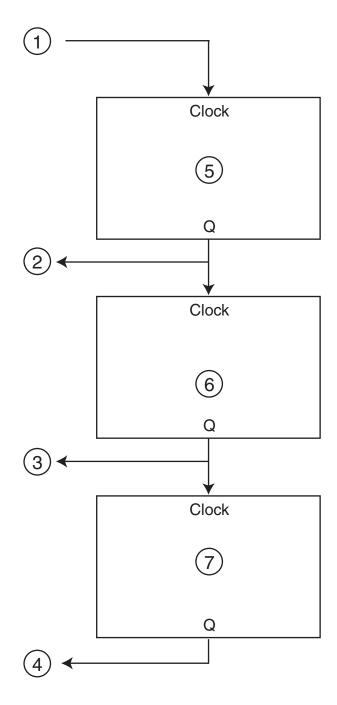

Figure 3.17 shows the functional block for a D-flip flop. The D input is sent to cell 1, the LD signal is sent to cell 2, and the Q output is sent from cell 3. When LD=0, Q is latched, while when LD=1, the D input is loaded into the feedback path. The ordered triple for this block is (2,19,9).

In this fashion, arbitrary functional blocks may be specified. Again, we have chosen a simple 3-cell block for this project, but it is relatively easy to implement larger-scale functional blocks, thereby decreasing the number of supercells required for a given target circuit.

In the current supercell design, we allow up to 64 different single cells which can be used to build a functional block. However, we have only defined twenty cells for the particular tests we ran. The choice of cells is unconstrained though, and whatever cells are needed for the anticipated desired circuits can be added to the supercell design.

The next section describes how the functional block's specification is encoded into the circuit's genome, and how the connections among those blocks are specified. Section 4 will discuss the cell-level encoding of the genome inside the supercell.

## 3.4.6 Circuit Genome

Each supercell contains a *genome* for the final desired target circuit. The genome is a coded description of the circuit, and contains two sets of information:

- 1. the functional blocks which will compose the nodes in the final circuit; and

- 2. the connections among the inputs and output of those functional blocks.

For the sake of genome specification, each node of the circuit is assigned a numeric node ID. The mapping from nodes to IDs is somewhat arbitrary. It may be helpful to number nodes which are closely connected with IDs which are numerically close, but this is not necessary, and in some cases doesn't even make sense.

| Cell Code | Configuration        | Description            |  |  |

|-----------|----------------------|------------------------|--|--|

| 1         |                      | DW->DE                 |  |  |

| 2         |                      | Input->DE              |  |  |

| 3         |                      | Input->DW              |  |  |

| 4         | <b>←</b>             | DW<->DE                |  |  |

| 5         | <b>—</b>             | DE->DW                 |  |  |

| 6         |                      | NOT                    |  |  |

| 7         |                      | AND                    |  |  |

| 8         | 1+                   | OR                     |  |  |

| 9         |                      | Flip Flop Feedback     |  |  |

| 10        | 10000000<br>00000000 | 1/128 Crystal          |  |  |

| 11        | CD                   | Crystal Controller     |  |  |

| 12        | 01010101<br>01010101 | High Frequency Crystal |  |  |

| 13        | D 1                  | Crystal Controller     |  |  |

| 14        |                      | Flip Flop Feedback     |  |  |

| 15        | CLK♥                 | Toggle Flip Flop       |  |  |

| 17        |                      | XOR                    |  |  |

| 18        | 1                    | Input->DW, DW->DE      |  |  |

| 19        | Q Q Select 0         | MUX                    |  |  |

| 20        | 700-                 | XNOR                   |  |  |

Figure 3.14

Functional Block Cell Codes

Figure 3.15 Supercell's Functional Block

Figure 3.16

Functional Block for NAND Gate with One Inverted Input

Cell codes are shown above each cell

Figure 3.17

Functional Block for D-Flip Flop

Clock is sent to middle cell's Southern input (block input #2)

D is sent to Western cell's Southern input (block input #1)

Q is sent to block's output

The one case in which the choice of node ID assignment is critical is for nodes which will interact with the outside world, i.e., nodes which should be accessed form outside the system. Since these nodes will need to be implemented by supercells along an edge of the Cell Matrix, they should be given the lowest node IDs (beginning with ID 1). This will be explained further in Section 4.

Each piece of the genome consists of a set of 6 numbers, describing:

- 1. the node number of this functional block:

- 2. the node number of the functional block supplying **this** node's first input;

- 3. the node number of the functional block supplying this node's second input;

- 4-6, the block numbers for this functional block's cells, as described above in Section 3.4.5

Figure 3.18 shows a sample circuit (the same one in Figure 3.13). Each node has been numbered with sequential numeric IDs, beginning with the input and output nodes. Note that the external output node has been assigned the same node number (1) as one of the input nodes. This is not a problem, since the external I/O lines are bidirectional.

Figure 3.19 shows the same circuit implemented as a set of interconnected functional blocks. For example, node 1's first input is sent to its external output (on the Western edge of cell 1); its external input (from the Western edge of cell 1) is sent to its  $f_{out}$  output. Node 4 receives its first input from node 1's output, and its second input from node 5's output. In this way, the circuit of Figure 3.18 is translated into a set of functional blocks with appropriate interconnects among them.

Figure 3.19 also shows the makeup of each functional block in terms of the cell code for each of the three cells in the block. For example, node 4 is composed of cells 2, 7 and 1, as specified in Figure 3.14

The circuit of Figure 3.19 can be translated directly into a genome, which simply noting the node numbers and cell codes of each block, and the sources for each block's inputs. Thus, the genome for this circuit is:

1,8,0,4,1,1, 2,0,0,1,1,1, 3,0,0,1,1,1, 4,1,5,2,7,1, 5,2,3,2,8,1, 6,4,3,2,19,9, 7,3,0,2,6,1, 8,6,7,2,17,1

Each row in the above list is called a *block*, and describes a single node in the final circuit. The first number of each block is the node's number, the second and third numbers are the node numbers of the nodes supplying inputs to this node, and the fourth through sixth numbers are the cell codes for this node's functional blocks, as shown in Figure 3.20. Note that unconnected inputs are specified with the special node number 0, which means "no connection."

The mapping from a circuit as in Figure 3.18 to a functional description as in Figure 3.19 is completely trivial to automate. For example, OrCAD Capture will translate schematic diagrams into Verilog, which is just a list of nodes and connections among nodes. Translating from a node such as "AND" to a standard triple of functional block cells such as "(2,7,1)" can also be easily automated, by using a simple lookup table. Therefore, it is relatively easy to automate the process of genome compilation from a schematic diagram, or from a text based language such as Verilog. However, creating such a compiler requires making firm decisions about what cells will be used to create functional blocks, how large functional blocks should be, and so on. For a proof-of-concept, it is thus easier to compile circuits into genomes by hand, as was done in this project.

Figure 3.18

Sample Final Target Circuit

Node numbers are shown above components.

Figure 3.19

Functional Block Numbering, Cell Codes and Interconnect for Circuit of Figure 3.18

Each block is indicated by a dashed rectangle.

Node number appears on the left (N:)

Cell codes appear on the right above each cell

| THIS NODE | FIRST<br>INPUT | SECOND<br>INPUT | FUNCTIONAL BLOCK |            | ОСК        |

|-----------|----------------|-----------------|------------------|------------|------------|

| Node      | Node           | Node            | Cell Code,       | Cell Code, | Cell Code, |

| Number    | Number         | Number          | Cell 0           | Cell 1     | Cell 2     |

## Figure 3.20 Genome Block Layout

Corresponds to a single node, whose number is given in the first segment.

Describes inputs to this node, as well as this node's functional block composition.

Functional Block Cell Codes are shown in Figure 3.14.

The complete genome consists of a number of these blocks,

one for each node in the final target circuit.

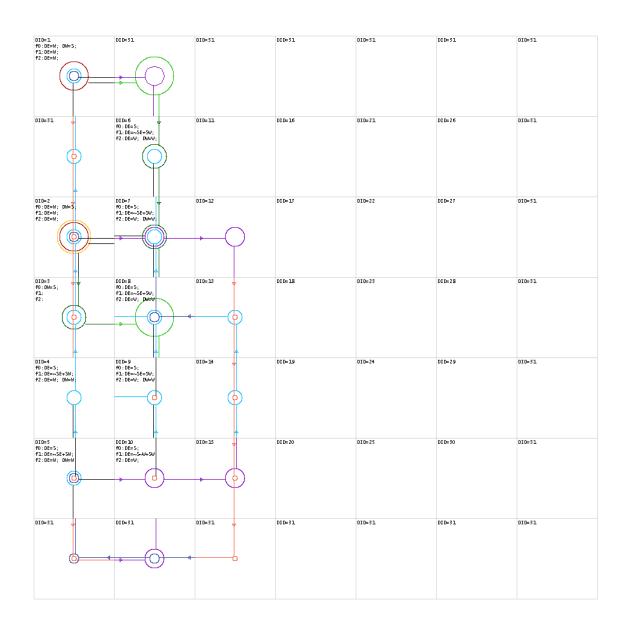

#### 3.4.7 Static ID Assignment

Since all nodes within the circuit are identified with numeric node IDs, there must be some way to assign a numeric node ID to each supercell within the supercell system. The easiest way to accomplish this is to use relative positional information. The IDs which are assigned in this way are called *Static IDs*, or *SIDs*, for reasons which will become apparent soon.

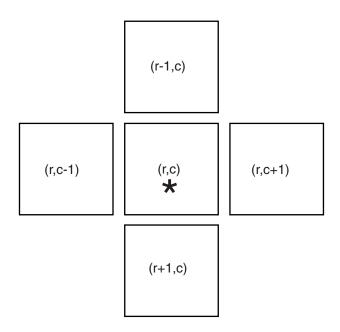

For simplicity, each SID can be viewed as an ordered pair (r,c), where r represents the row in which the supercell sits and c represents the column, both relative to the first (upper-leftmost) supercell. The first supercell is hardwired to have an SID of (1,1). All other supercells dynamically assign themselves SIDs based on the SIDs of any adjacent supercells. In Figure 3.21, the supercell labeled "\*" has been assigned SID (r,c), based on the SID of its neighboring supercells. For example, the supercell to the left has SID(r,c-1). Since supercell "\*" is in the next column to the right, it's SID is (r,(c-1)+1).

Of course, the supercell "\*" will also note that the supercell to its right has SID (r,c+1), and, based on that, will want to assign itself SID (r,(c+1)-1). Similar comments apply to the SID received from above and below. However, all four dynamic SID calculations result in the same final SID, (r,c).

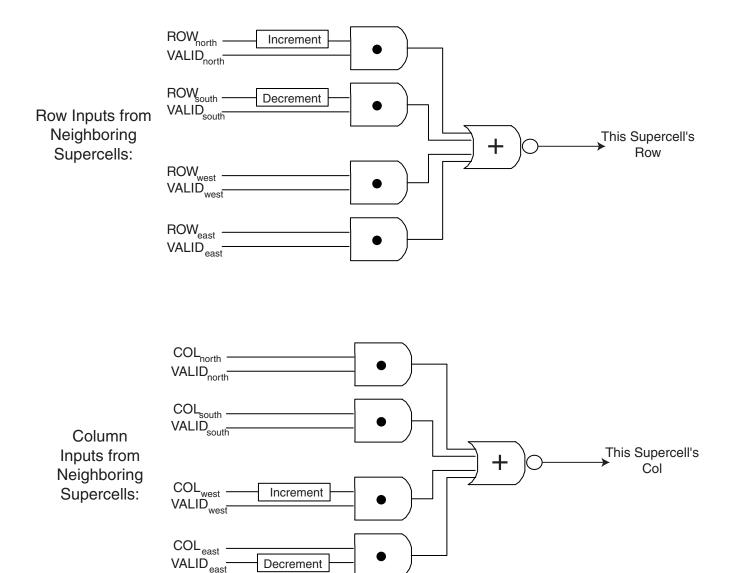

Figure 3.22 shows a piece of the circuit for performing this SID calculation. Note that each side receives not only r and c, but also a VALID signal from each adjacent supercell<sup>4</sup>. The circuit makes the necessary adjustment (increment or decrement) on either r or c, and then zeros out all the bits if VALID is false. The results from all four sides can thus be bitwise-ORd to produce the final (r,c) for this supercell. This final (r,c) SID is then transmitted to adjacent supercells, so that they may further arbitrate their own SIDs.

It is important to note that, if each supercell were to transmit and receive to all of its adjacent supercells, one would create self-feeding loops wherever a 1 was transmitted between two supercell. This situation is avoided by using the Link Lock network (Section 3.4.3 above). SIDs are input from all sides, but are only transmitted on sides where a LINK output is asserted. If there is no LINK output, a serial stream of all 0s will be effectively transmitted, which will be interpreted as INVALID by the receiving supercell, and thus ignored in SID calculations.

It is also important to note that there will always be at least one pathway to each supercell within the system. If there was no pathway available on the L2 network, then there would be no way for the supercell to have been created in the first place.

The numeric data for r and c are transmitted as serial bitstreams. These are sent LSB first, which is important for incrementing/decrementing them. Note that all supercells perform these same operations on the same bits of the bitstream at the same time. In other words, all supercells will process bit 0 of the SID bitstream at the same time, adding or subtracting one, comparing to neighboring supercell's SIDs, and so on. Then all supercells will proceed to bit 1, conditionally changing that bit, and so on. Thus, other than propagation delay, the time required to assign SIDs is independent of the number of supercells, and depends only on the number of bits in the SID serial bitstream.

## 3.4.8 Dynamic ID Assignment

The above scheme for assigning SIDs works quite well, but there is one problem. Because SIDs are based on positional information, there is no guarantee that a particular SID will be present in the final set of supercells. For example, in Figure 3.23, the middle supercell in a 3x3 set has not been configured, because of the presence of a hardware fault within that region. Therefore, there is **no** supercell with SID (2,2).

Therefore, if we used SIDs inside our genome, and we assign a node to SID (2,2), that node would be missing in the final circuit, and our circuit would not work. The problem is that the genome encoding must be location-independent, while SIDs are extremely location dependent.

<sup>&</sup>lt;sup>4</sup> In the actual circuit implementation, r and c are sent in as a single serial bitstream, proceeded by a VALID bit.

Figure 3.21

Supercell "\*" can compute its (r,c) address from the address of any of its neighboring supercells. If multiple neighboring supercells are available, all computed addresses should end up identical.

Decrement

Figure 3.22 Row and Column calculation inside a Supercell Su[ercell can compute its own row and column by adjusting the row and column information provided by neighboring supercells.

The VALID signals are 0 if there is no neighboring supercell.

| (1,1) | (1,2) | (1,3) |

|-------|-------|-------|

| (2,1) | *     | (2,3) |

| (3,1) | (3,2) | (3,3) |

Figure 3.23

3x3 Set of Supercells with Missing Supercell in Middle

Because static IDs (shown inside each supercell) are position-based,

NO supercell has been assigned Static ID (2,2)

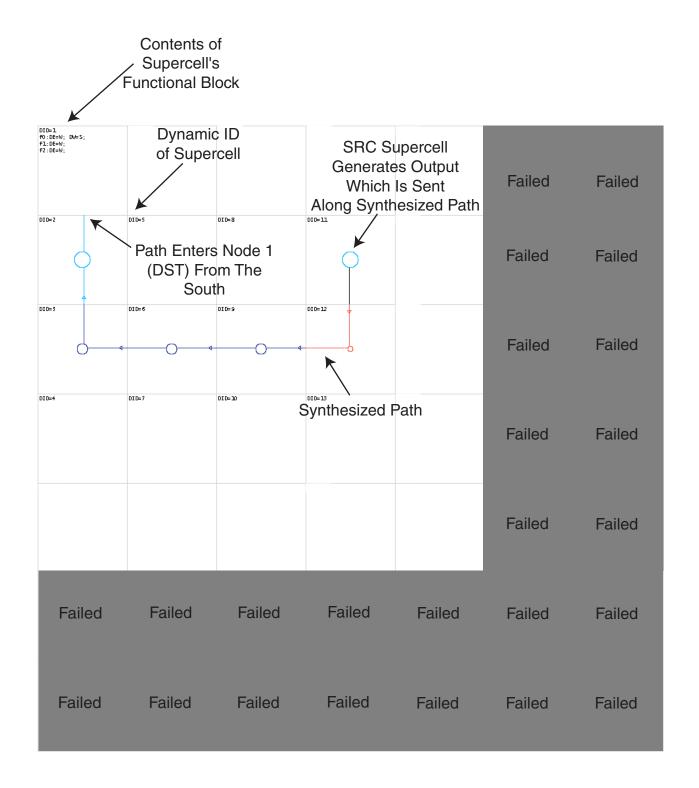

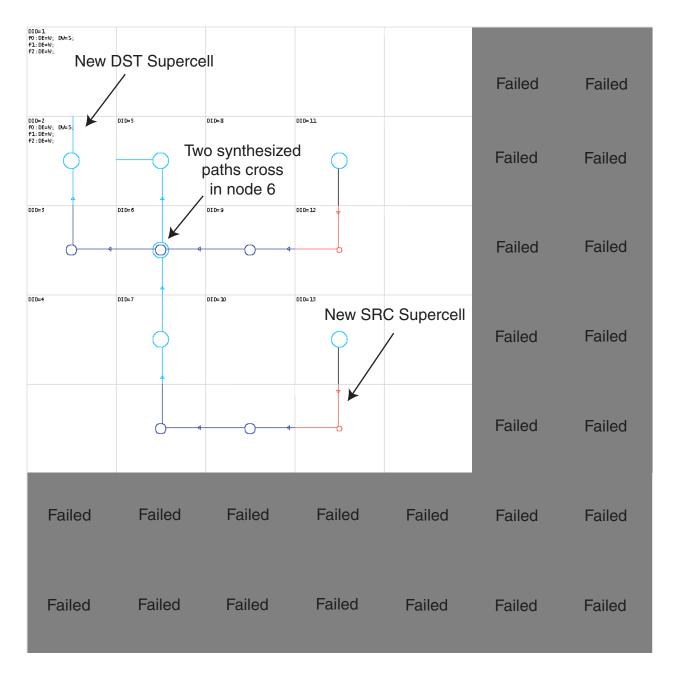

The solution to this problem is to assign *Dynamic IDs*, or *DIDs*, to each supercell, such that the set of assigned DIDs begins with 1 and has no gaps. In this way, if we have say at least eight supercells in our final system, we will be guaranteed that we have DIDs of 1, 2, 3, 4, 5, 6, 7 and 8. We therefore only need to have at least as many functioning supercells as we have nodes in our circuit. The location of those nodes becomes irrelevant.

To achieve this DID assignment, we require a mapping from SID→DID such that the set of assigned DIDs is contiguous. One way to achieve such a mapping is to simply order the SIDs and the desired DIDs, and then map them in that order (first SID→ first DID, second SID→ second DID, and so on).

The supercells are able to dynamically perform this mapping by themselves. To achieve this, they assign themselves a single integer value based on their SID(r,c), using the formula

$$(r,c) \rightarrow 2^{32} * c + r.$$

The resulting integers thus supply an ordering to the SIDs of each supercell.

The set of supercells assign themselves DIDs using the following algorithms:

- 1. Determine the smallest SID among all supercells which have **not** been assigned a DID

- 2. Assign that supercell the next consecutive DID (beginning with 1)

- 3. Repeat until there are no supercells with unassigned DIDs

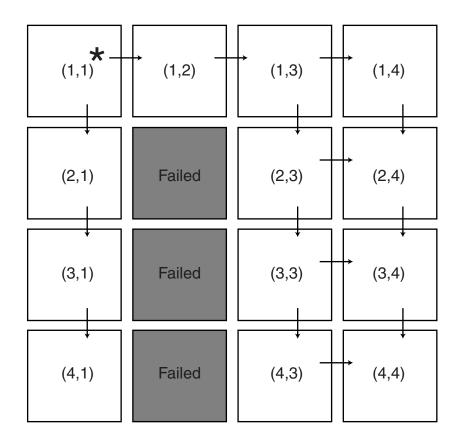

The only tricky part of this algorithm is step 1. To determine the smallest SID, a parallel comparison is performed among all unassigned supercells. Specifically, each supercell compares its own SID with any SIDs being sent by neighboring supercells. The minimum SID of this set of SIDs is then broadcast to all adjacent supercells. However, unlike the SID assignment, this broadcast is only done along the **reverse** direction of the LINK outputs in the L2 network. Figure 3.24 illustrates the situation. The arrows show the LINK outputs, as would be present in an L2 network initiated from the supercell (1,1) in the upper left corner. For example, supercell (3,3) generates a LINK output signal to both the supercells (4,3) and (2,3).

In this configuration, supercell (3,3) would compare SIDs being sent by supercells (4,3) and (3,4) to its own SID, and would transmit the minimum SID to supercell (2,3). Note again that these transmission are occurring in the backwards direction along each LINK output. Also, each supercell only compares its own SID if it itself has not yet been assigned a DID. Otherwise, the comparison is only made on the incoming SIDs.

With each supercell acting in this fashion, the result is that the initiator of the L2 network (supercell (1,1)) can determine the global minimum SID by comparing the SIDs it is receiving (and possibly its own SID). The minimum of that comparison will be **the** minimum of all unassigned supercells' SIDs in the system.

Next, supercell (1,1) broadcasts this minimum SID to all other supercells along the L2 network (in the forward direction along the LINK output lines). Each supercell receives this minimum SID, and compares it to its own SID. If all bits match, then that supercell knows it has the minimum SID, and it assigns itself the next consecutive DID. Proceeding in this way, all supercells are assigned DIDs.

There are some important details which should be noted here:

- To compare the magnitude of two serial bitstreams, it is best to transmit the streams MSB first. With that ordering, as soon as the two streams differ, the stream containing a 0 is know to be smaller than the stream containing the 1. However, SIDa were generated LSB first for efficient increment/decrement operations. Therefore, each supercell contains a **bit reversal** circuit, which transposes bits within a serial bitstream. This is a simple circuit which simply captures bits, and replays them in a reversed order.

- Since comparisons can be made on a bit-by-bit basis, there is no looping in this minimum-SID calculation. Rather, the first bit of **all** unmapped SIDs are compared simultaneously, and the first bit of the global minimum is known immediately. Thus, again, except for propagation delays, the time to compute this first bit is independent of the number of supercells under consideration. Similar

Figure 3.24

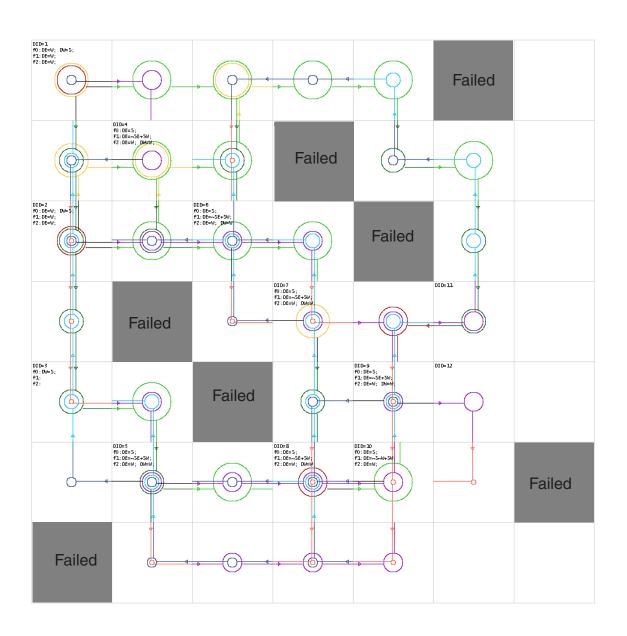

DID Arbitration in a 4x4 set of supercells with 3 failed regions

Arrows show LINK outputs on a Link/Lock network initiated from supercell (1,1) ("\*")

DID comparison flows in reverse arrow direction

- comments apply for the second bit, the third bit, and so on. Thus the time required to determine the global minimum SID is a function of the SID length, not the number of SIDs being compared <sup>5</sup>.

- As soon as supercell (1,1) has determined the first bit of the global minimum SID, and broadcast this bit to all supercells, each supercell can compare that bit to its own SID's first bit, and determine if it is still a candidate for being the global minimum. In this way, once the global minimum SID has been completely determined, the supercell with the matching SID has also been determined. There is no need for an additional comparison step for the matching supercell to identify itself. The comparison is performed at the same time that the global minimum SID is being computed.

- Each supercell retains a copy of the next DID to assign, and increments it after each step of this algorithm. Thus, there is no need to broadcast the next DID to all supercells. Each supercell retains its own copy of this variable. This is an example of distributing the processing throughout the hardware, rather than performing the processing in one location and distributing the data. It is a key advantage of fine-grained reconfigurable hardware over traditional memory/CPU systems.

- As with SID assignment, supercells will on appear in the system at all unless there is an L2 path to them. Therefore, all supercells will eventually be assigned DIDs with this algorithm.

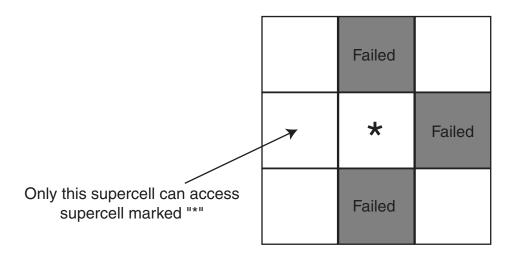

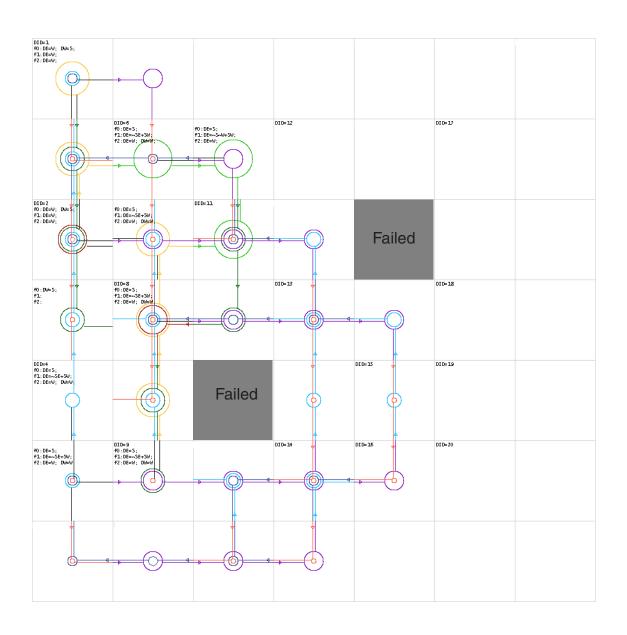

There is one further enhancement to the above algorithm. In our research, we learned that assigning nodes to supercells which are adjacent to failed regions makes circuit construction more difficult. For example, in Figure 3.25, the supercell labeled "\*" has failed cells on three sides. As a result, connections to and from "\*" can only be made through one side of that supercell, namely via the supercell to its left. If "\*"'s output was being sent to many other nodes, it would be difficult to implement this routing.

To account for this situation, we have implemented additional circuitry which detects the presence of failed regions in adjacent locations. During DID assignment, if any adjacent region is marked as FAILED (i.e., does not contain a properly-working supercell), then the supercell will remove itself from consideration as a global minimum SID. In Figure 3.26, the supercell marked "\*" will detect missing supercells around it, and therefore "\*" will not allow itself to be considered in the minimum SID algorithm. In fact, only the supercells marked with "+" are now candidates for being global minimum SIDs, and therefore are the only supercells which will eventually have DIDs assigned. The result is that an expanded region (indicated by the darkened line in Figure 3.26) is created around the actual failed regions, and no DIDs will be assigned to supercells within this expanded region. Note however that the good supercells which are not assigned DIDs **can still** be used for building connections among supercells. The algorithm does **not** discard supercells next to failed regions. It merely avoids assigning DIDs to those supercells, i.e., it does not assign those supercells to act as nodes in the final target circuit.

This feature, which is called *edge sensing*, can be enabled or disabled by changing the configuration of a single cell within the final supercell circuit.

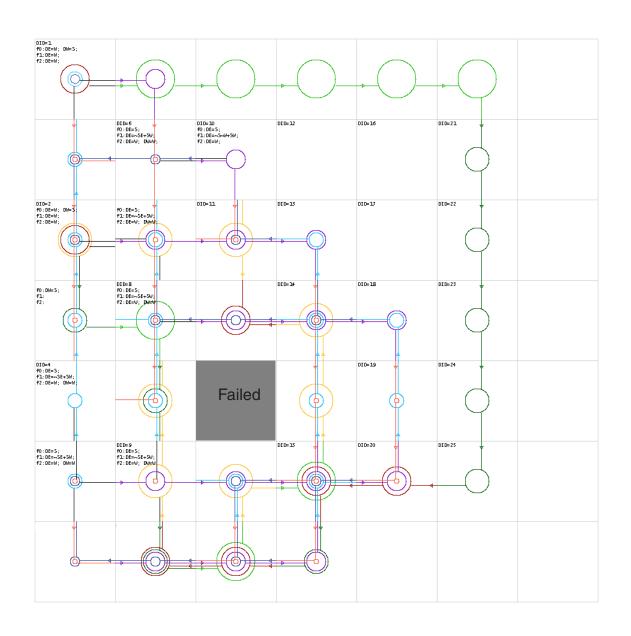

# 3.4.9 Traceback Generation and Parsing

Once DIDs have been assigned to all supercells, the next step in circuit assembly is to process the circuit genome. Each piece of the genome contains 4 pieces of information:

- 1. the DID of the node (called the DST node) described by this piece of the genome;

- 2. the DID of the node (called the SRC1 node) supplying the DST node's first input;

- 3. the DID of the node (called the SRC2 node) supplying the DST node's second input; and

- 4. the coded description of the DST node's functional block.

Synthesis of the functional block has already been described (Section 3.4.5 above). What remains in order to implement the target circuit it to build the pathways from the SRC nodes to the DST nodes via the supercell network. The actual path synthesising mechanism will be described in Section 3.4.10 below. However, before pathways can be built, the system must determine exactly what path to use to transmit data from a SRC node to a DST node. The method of determining such a pathway is called *traceback generation*.

<sup>&</sup>lt;sup>5</sup> This is a fundamental characteristic of circuits built on the Cell Matrix. The ability to create circuits which operate efficiently in parallel instead of looping sequentially is a recurring theme in Cell Matrix circuit design.

Figure 3.25

Effect of failed regions on supercell access

Supercell "\*" can only be accessed from one side.

This is a potential problem if "\*" implements a node

whose output is used by many other nodes

(and therefore needs lots of pathways connected to it).

| + |   | Failed |        | + | + | + |

|---|---|--------|--------|---|---|---|

| + | + | *      | Failed |   | + | + |

| + |   | Failed |        | + | + | + |

| + | + |        | +      | + | + | + |

| + | + | +      | +      | + | + | + |

Figure 3.26

Edge Sensing in a network of supercells with failed regions

"\*" can only be accessed from one side, and therefore should not

be used to implement a node in the genome.

Edge Sensing causes supercells adjacent to failed regions to NOT be assigned DIDs (indicated by lack of "+" inside). Therefore, all interior supercells which ARE assigned DIDs ("+") are guaranteed to be surrounded by functioning supercells.

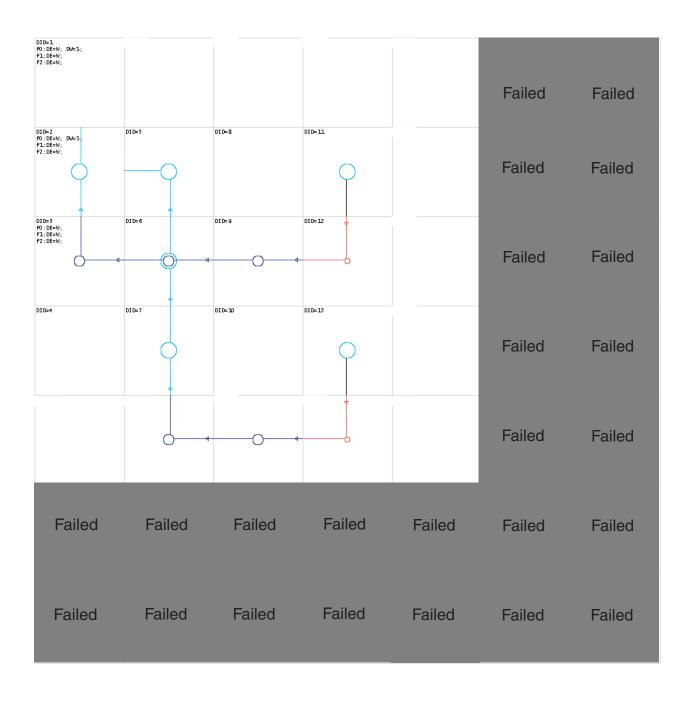

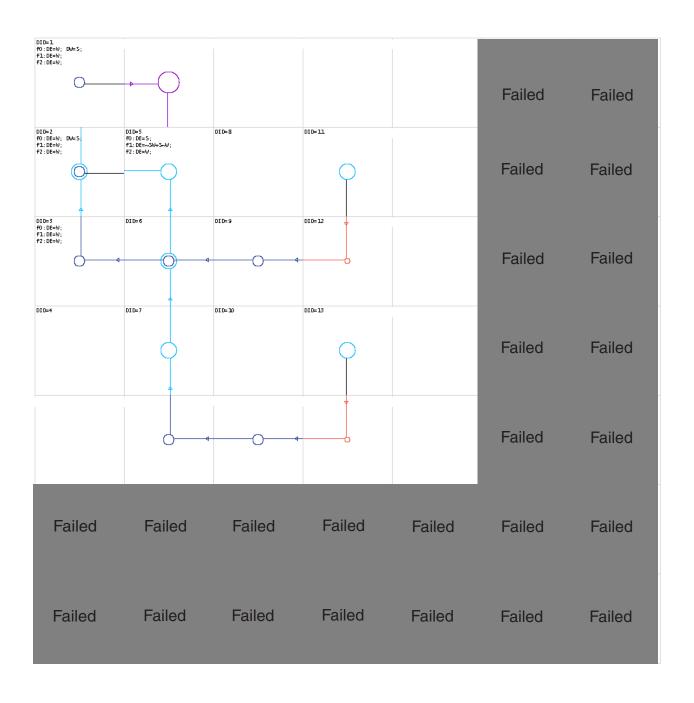

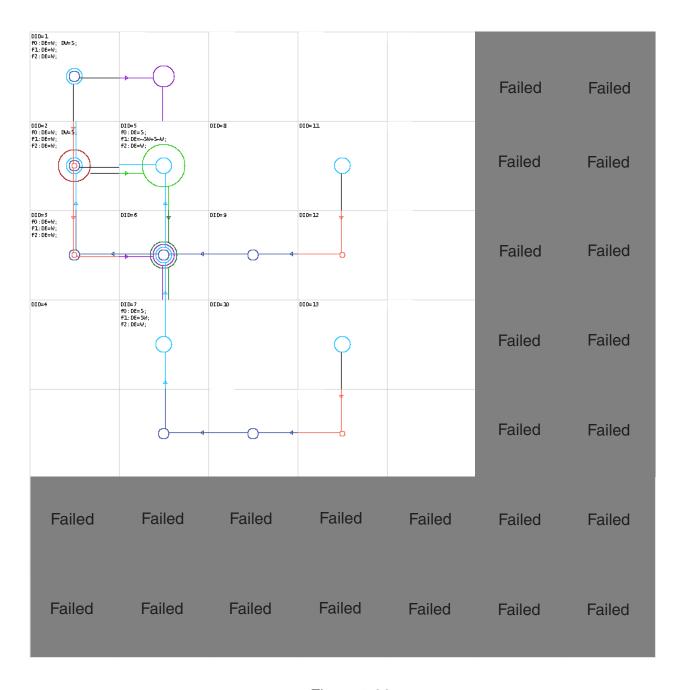

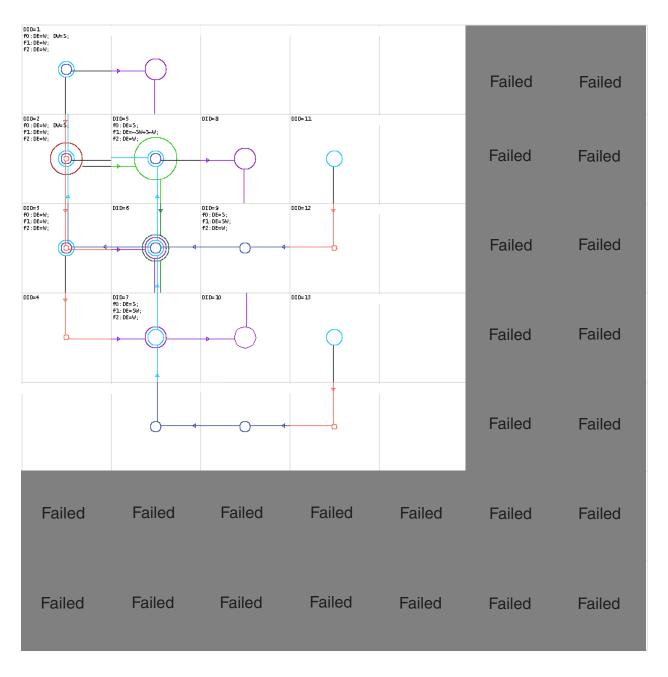

Each supercell contains its own (identical) copy of the final circuit's genome. This genome is basically a prescription for how to assemble the target circuit, with each block of the genome (Figure 3.20) describing a single DST node's inputs and its functional behavior. By successively processing each of these genome blocks, the final circuit is assembled, one node at a time.

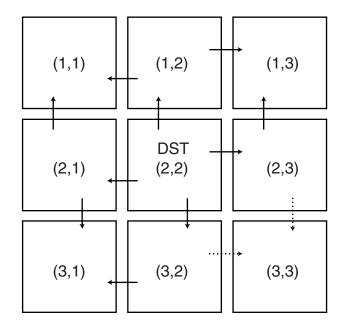

Each supercell also maintains a *current block* pointer, indicating which block is being processed. This pointer is advanced simultaneously in all the supercells, so that all supercells are always processing the same genome block at any given time. By using the current block pointer to pick a genome block, **all** supercells know the DID of a current DST node, as well as the DIDs of the SRC1 and SCR2 nodes to be connected to the DST node's inputs.

Traceback generation begins with each supercell comparing its own DID to the current genome block's DST. Exactly one supercell should recognize the DST DID as matching its own DID. That supercell now becomes the DST node.

The DST node next assembles a Link/Lock (L2) network, beginning with itself, and broadcasting to all reachable supercells in the supercell collection. Depending on the presence of already-built pathways among the supercells, not all supercells will be reachable. There are only a finite number of connections possible between two supercells. In Figure 3.27, pathways have previously been built from  $(3,2) \rightarrow (3,3)$  and from  $(2,3) \rightarrow (3,3)$ . These are shown by the dotted lines. The L2 network subsequently built from DST node (2,2) is shown in solid lines. (2,2) can access all supercells except (3,3), since the two sides from which (3,3) can be accessed are in use. Note that this is a deliberately simplified example. In the actual supercell implementation, it is possible to access each supercells via **three**<sup>6</sup> independent channels on each side. Thus, a typical (internal) supercell can be accessed via 12 different paths (4 sides \* 3 channels per side). See Section 3.4.10 below for more details on channels.

After the DST node has assembled its L2 network, it sends a signal (via that L2 network) to all connected supercells, requesting initiation of a traceback. At this point, all supercells (which, recall, each have a copy of the current genome block) compare their DID to the SRC1 DID<sup>7</sup>. The supercell which matches declares itself the SRC1 node. Upon receiving the traceback request from DST, SRC1 broadcasts a *traceback string*, using the reverse LINK outputs of the L2 network (exactly as in the DID assignment, Section 3.4.8). Note that since SRC1 received the traceback request, there is guaranteed to exist at least one pathway from DST to SRC1 on the current L2 network. All that remains is for DST to discover exactly what that pathway is.

Figure 3.28 shows a particularly unpleasant 5x5 collection of supercells. Supercells which are grayed out are missing, presumably because of hardware failures. DIDs are indicated inside each supercell (we're assuming edge sensing, as described at the end of Section 3.4.8, has been disabled). Node 5 is DST, and node 15 is SRC1. The L2 network, constructed from node 5, is indicated by the arrows from supercell to supercell. When SRC1 receives the traceback request, it broadcasts a single *Valid* bit in the reverse direction of all arrows coming into it.

Each supercell which receives this valid bit performs the following steps:

- notes the direction D the valid bit arrived from<sup>8</sup>;

- broadcasts the valid bit to its adjacent supercells (again on the reverse LINK outputs);

- broadcasts a coded representation of direction D to all adjacent supercells (again in the reverse LINK outputs);

- broadcast any remaining data received following receipt of the valid bit.

<sup>6</sup> The choice of using three channels is somewhat arbitrary. The design can easily be extended to allow more channels.

<sup>&</sup>lt;sup>7</sup> In this section we will describe traceback generation from DST to SRC1. This is then followed by path synthesis between those nodes. Following that, the entire process (traceback generation and path synthesis) is repeated for the DST $\leftarrow \rightarrow$  SRC2 pathway.

<sup>&</sup>lt;sup>8</sup> If a valid bit is received from more than one side, a priority ordering is used to pick a single side. The current ordering is N (highest priority), S, W, E (lowest priority). This ordering can be randomized for increased flexibility-see Section 7.

Figure 3.27

Example of Routing Contention

Supercell at (2,2) "DST" has initiated a Link/Lock network

Supercells (3,2) and (2,3) already have pre-existing paths built to (3,3),

shown by the dashed lines. Therefore, DST's L2 network can not reach (3,3).

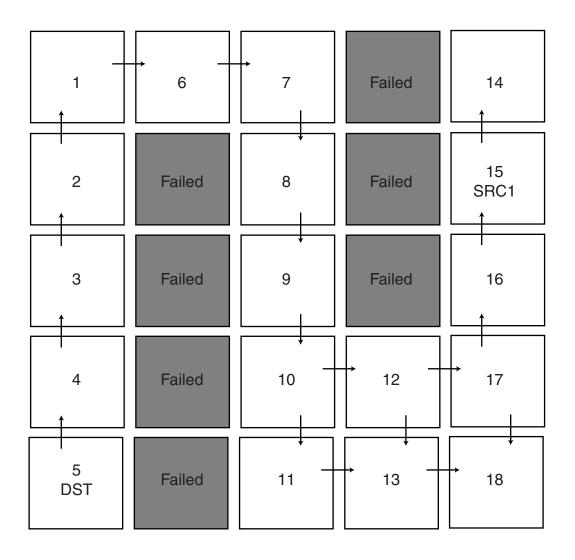

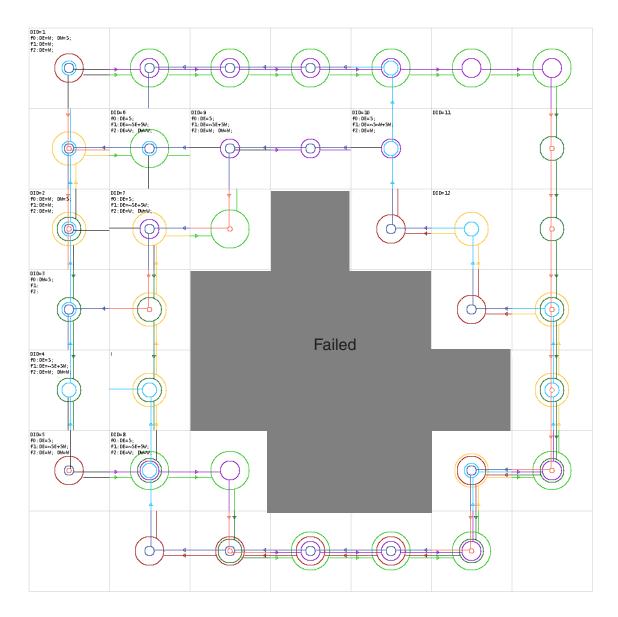

Figure 3.28

Link Lock Network in set of 5x5 Supercells with Failed Regions

Network has been generated by DST supercell

Dynamic IDs (DIDs) are shown inside each supercell

Arrows indicate LINK outputs

The effect of this algorithm is that each node appends the arrival direction D to the beginning of the traceback string, and re-broadcasts the traceback string, with a valid bit in the beginning.

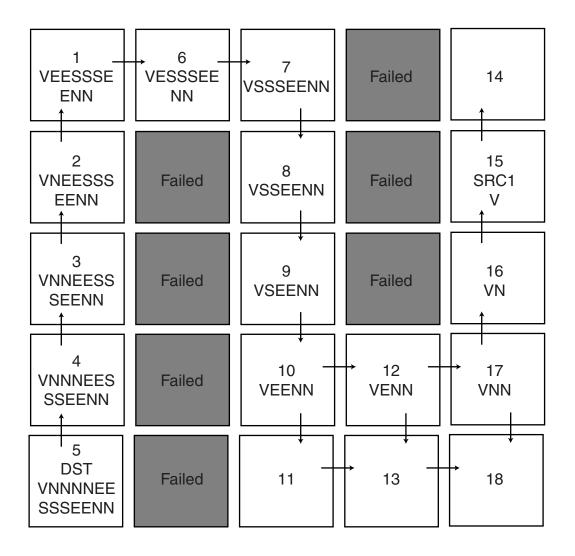

An example will help to clarify this. In Figure 3.29, the string shown inside each node represents the string it broadcasts to adjacent nodes. Node 15 is SRC1, and thus broadcasts a valid bit "V" to node 16.

Node 16 receives a valid bit (from node 15), and then performs the above steps. It notes that V was received from the North ("N"), then broadcasts the valid bit, followed by "N." No other data is received by node 16, thus its full transmission is the string "VN." This will be broadcast to node 17.

Node 17 receives the string "VN," notes its arrival from the North, broadcasts a valid bit V, the direction "N," and finally the remaining received string "N." Thus node 17's full transmission is "VNN." This will be broadcast to node 12. Note that node 18 does not receive a traceback string. This indicates that, on the current L2 network, node 18 has no pathway to node 15. This is not a problem, as node 5 is the initiator of the L2 network, and thus only connectivity from node 5 to other nodes is important.

Node 12 receives the string "VNN" and notes that it arrived from the East. It then broadcasts a valid bit V, followed by "E," followed by the remaining data it receives, in this case the string "NN." Thus node 12 broadcasts the string "VENN."

Looking at this string closely, we see that it is simply a map for traversing the supercell network to arrive at SRC1 from node 12. Thus, from node 12, you can reach SRC1 by moving East (to node 17), then North (to node 16) and then North (to node 15).

In a similar manner, node 10 receives "VENN" and broadcasts "VEENN." Node 9 broadcasts "VSEENN" and so on. Finally, node 5 will receive the string "VNNNEESSSEENNN" from node 4. Node 5 notes the arrival direction (N), inserts that after the valid bit, and thus has the full traceback string "VNNNNEESSSEENNN." This is a complete map of how node 5 can reach node 15 in the current L2 network.

The DST supercell stores this traceback string in an internal memory (actually all supercells store their traceback string). DST can then parse this string, one character at a time, and build a pathway between itself and SRC1. The path synthesis mechanism is explained in the next section.

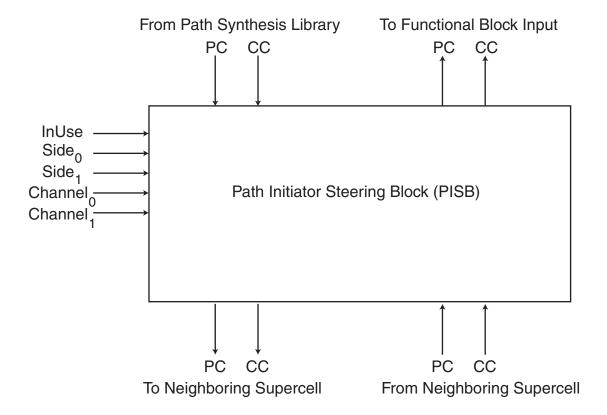

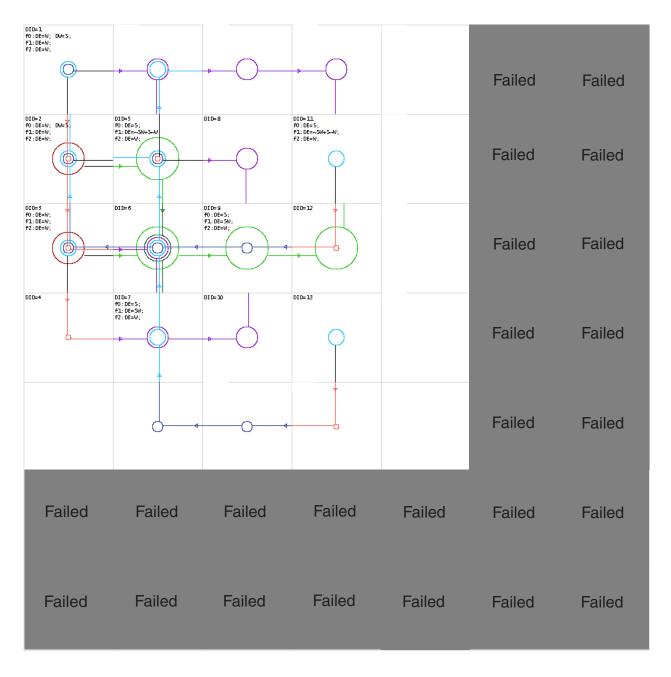

# 3.4.10 Path Synthesis and the Steering Block

Ultimately, supercells need to exchange information with one another. To do so, pathways must be built among the supercells. Since the supercell is the basic atomic unit for the finished circuit, and since only hardware covered by supercells can be guaranteed to be defect free, the pathways must actually be built **through** the supercells. The easiest way to accomplish this is to include pre-existing path segments inside each supercell. These segments handle the actual transmission of data through one supercell. Steering of the path is accomplished by dictating on which side of the supercell each segment exits.

The self-configurability of the Cell Matrix can be put to good use to accomplish this. The supercells include circuits which are called *multi-channel wires*, and are disclosed in a pending patent applications (allowed July 2001) (Mac 2001). Such wires are used to transfer binary data from one cell to another, such as is needed for implementation of the final target circuit. However, multi-channel wires can also carry cell configuration information to the cells at the end of the wire. And, because of the self-configurability of cells, multi-channel wires can carry configuration information **for building more multi-channel wires**. In this fashion wires can be efficiently extended.

The process of path synthesis is thus a sequence of wire configuration steps, where each configuration builds a path from the current supercell to the desired next supercell. This process, dictated by the traceback string, continues until the desired cell (SRC1) has been reached. Following this, SRC1 may send data to DST along the just-constructed path (the paths are bidirectional).

Figure 3.29

Traceback Generation using same Link Lock Network from Figure 3.28

Traceback packets are passed in the **reverse** direction of the LINK outputs (arrows).

Current traceback string **to be broadcast** is shown inside each supercell.

V is the valid signal. Other characters show directions.

Final traceback string is NNNNEESSSEENN.

As mentioned above, it is desirable to have pre-existing wire segments inside each supercell, rather than trying to build a complete path from one end of a supercell to another. This is not only faster, but is also much easier, since building wires through already-existing circuitry can be difficult.

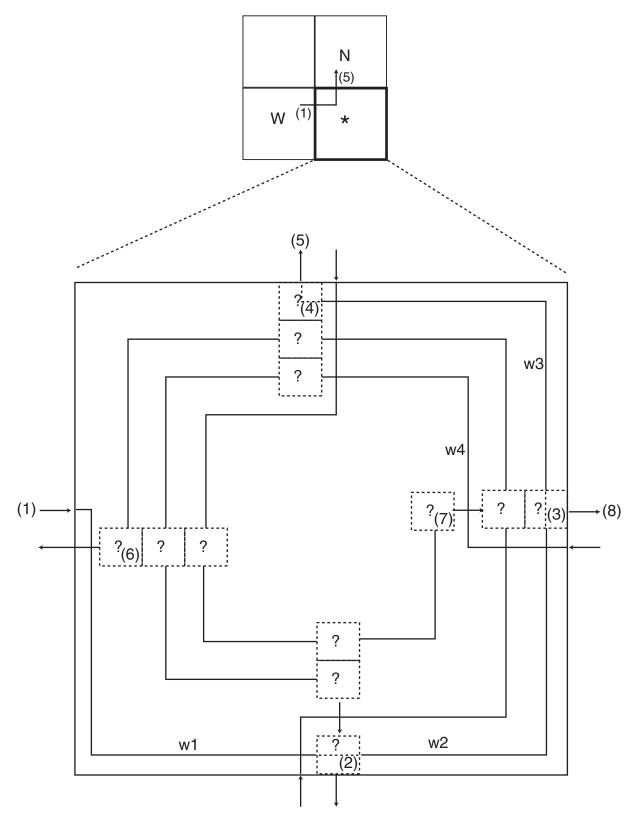

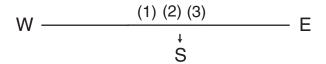

Figure 3.30 illustrates a supercell containing a circuit called a *steering block*, which is used for extending paths through the supercell. The inputs and outputs along the edges represent incoming and outgoing paths. Tiling these supercells connects inputs to outputs, and vice versa. The paths inside the steering block are actually multi-channel wires, capable of carrying data as well as being extended. The areas marked with "?" are breaks in the wires (unconfigured cells). Figure 3.30 also shows a 2x2 array of supercells, containing this supercell ("\*"), another supercell to its West ("W") and another to its North ("N"). We're ignoring the supercell in the upper left.

Suppose now that W's traceback string is telling it to build the indicated path: East, then North. W's Eastern output is connected to point (1) in Figure 3.30. Therefore, by outputting configuration commands to its Eastern output, W has access to a wire inside \*'s steering block. In particular, it has access to the unconfigured cells in region (2) of \*.