### Self-Modifying Circuitry for Efficient, Defect-Tolerant Handling of Trillion-Element Reconfigurable Devices

Nicholas J. Macias

Dissertation submitted to the Faculty of the

Virginia Polytechnic Institute and State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering

Peter M. Athanas, Chair

Cameron D. Patterson

Tom L. Martin

A. Lynn Abbott

Alex K. Jones

April 2011

Blacksburg, Virginia

Keywords: reconfigurable, self-configurable, self-modifying, FPGA, parallelism, fault handling, non-dualism, Avogadro machine

Copyright ©2011 Nicholas J. Macias

Self-Modifying Circuitry for Efficient, Defect-Tolerant Handling of Trillion-Element Reconfigurable Devices

Nicholas J. Macias

(ABSTRACT)

As VLSI circuits continue to have more and more transistors over time, the question of not only how to use, but how to manage the complexity of so many transistors becomes increasingly important. Four hypothesis are given for the design of a system that scales-up as transistors continue to shrink. An architecture is presented that satisfies these hypothesis, and the motivation behind the hypothesis is further explained. The use of this architecture's unique features to implement an efficient, defect-tolerant parallel bootstrap system is discussed. A detailed methodology for implementing this system in vivo is described. A sample problem — simulation of heat flow — is presented, and its solution using the proposed architecture is described in detail. A comparison is made between the proposed architecture and a set of contemporary architectures, and the former is shown to have desirable performance in a number of areas. Conclusion are given, and plans for future work are presented.

## Dedication

To everyone who's ever lived, loved or dreamed outside the lines, this is humbly dedicated.

## Acknowledgments

The author wishes to thank Peter Athanas for his guidance, wisdom, and patient review of this work and manuscript. The author is also indebted to the other committee members — Cameron Patterson, Tom Martin, Lynn Abbott and Alex Jones — for their participation in the various stages leading up to and including the final defense.

## Contents

| 1 | Intr | Introduction                       |    |  |  |  |  |

|---|------|------------------------------------|----|--|--|--|--|

|   | 1.1  | Hypothesis about future computing  | 8  |  |  |  |  |

|   | 1.2  | Prior Art                          | 11 |  |  |  |  |

|   | 1.3  | Bio-Inspiration                    | 11 |  |  |  |  |

|   | 1.4  | Scope                              | 12 |  |  |  |  |

|   | 1.5  | Organization of paper              | 13 |  |  |  |  |

| 2 | Bac  | ackground                          |    |  |  |  |  |

|   | 2.1  | Large-Scale Reconfigurable Systems | 16 |  |  |  |  |

|   |      | 2.1.1 A Scalable Design            | 19 |  |  |  |  |

|   | 2.2  | Internal Control                   | 28 |  |  |  |  |

|   | 2.3  | Configurable Control Systems       | 34 |  |  |  |  |

|   | 2.4 | Hierar  | chy-Free Organization                              | 37  |

|---|-----|---------|----------------------------------------------------|-----|

|   |     | 2.4.1   | Subject/Object Non-dualism                         | 38  |

|   |     | 2.4.2   | Application of Non-Dualism to Architectural Design | 45  |

| 3 | Par | allel F | ault Testing and Configuration                     | 57  |

|   | 3.1 | Config  | guration Issues                                    | 58  |

|   | 3.2 | Parall  | el Self-Configuration: Medusa Blocks               | 64  |

|   |     | 3.2.1   | Extensible Wires                                   | 65  |

|   |     | 3.2.2   | Synthesis of a PCS on a Perfect Substrate          | 67  |

|   |     | 3.2.3   | Construction of a PCS on an Imperfect Substrate    | 75  |

|   |     | 3.2.4   | Synthesis of Target Circuit                        | 80  |

|   | 3.3 | Detail  | ed Description of Medusa Block                     | 87  |

|   |     | 3.3.1   | Signal Transmission Network                        | 89  |

|   |     | 3.3.2   | Extension Mechanism                                | 92  |

|   |     | 3.3.3   | Fault testing                                      | 94  |

|   |     | 3.3.4   | Fault Isolation                                    | 98  |

|   |     | 3.3.5   | Detecting Neighboring Blocks                       | 100 |

|   |     | 3.3.6   | Activate/Progesss Signal Pair                      | 102 |

|   |     | 3.3.7  | Configuration of New Blocks               | 103 |

|---|-----|--------|-------------------------------------------|-----|

|   |     | 3.3.8  | Cell Configuration in the $Z=1$ Plane     | 105 |

|   | 3.4 | Simula | ation                                     | 108 |

|   |     | 3.4.1  | Sequences and Supersequences              | 111 |

|   |     | 3.4.2  | Potential for Pathological Sequences      | 113 |

|   |     | 3.4.3  | Keeping Simulation Feasible               | 114 |

| 4 | Sup | ersequ | ence Generation                           | 115 |

|   | 4.1 | Block- | elevel Descriptions                       | 116 |

|   |     | 4.1.1  | Single-Sequence Generator Block           | 116 |

|   |     | 4.1.2  | Counter Block                             | 118 |

|   |     | 4.1.3  | Supersequence Generation, Block Level     | 119 |

|   | 4.2 | Supers | sequence Generator Details                | 124 |

|   |     | 4.2.1  | PC and CC Store and Selectors             | 124 |

|   |     | 4.2.2  | Counter Block                             | 129 |

|   |     | 4.2.3  | CC Shifter, Latch, and Timing Control     | 132 |

| 5 | San | nnle A | pplication: Solution of the Heat Equation | 135 |

|   | 5.1 | Heat Equation Background                                   | 135 |

|---|-----|------------------------------------------------------------|-----|

|   | 5.2 | Finite Element Method as Applied to the Heat Equation      | 137 |

|   | 5.3 | Modelling Thermal State in a 2-D Region                    | 138 |

|   | 5.4 | Circuit/Cell-Level Description of 2-D Heat Equation Solver | 142 |

|   | 5.5 | Simulation and Results                                     | 146 |

|   | 5.6 | Extension to 3-D                                           | 151 |

|   | 5.7 | Comment on 3-D wiring efficiency                           | 157 |

| 3 | Con | nparative Analysis                                         | 164 |

|   | 6.1 | How Large?                                                 | 164 |

|   | 6.2 | Viability                                                  | 167 |

|   | 6.3 | Speed                                                      | 170 |

|   | 6.4 | Reliability                                                | 173 |

|   |     | 6.4.1 Manufacturing Defects                                | 174 |

|   |     | 6.4.2 Runtime Upsets                                       | 176 |

|   | 6.5 | Setup Time                                                 | 177 |

|   | 0.0 |                                                            |     |

|   | 6.6 | Cross-Sectional Bandwidth                                  | 179 |

| 7 | 7 Conclusions and Future Work |    |  |  |  | Conclusions and Future Work |  |  |  |

|---|-------------------------------|----|--|--|--|-----------------------------|--|--|--|

|   | 7.1 Conclusions               | 18 |  |  |  |                             |  |  |  |

|   | 7.2 Future Work               | 18 |  |  |  |                             |  |  |  |

# List of Figures

| element communicates with a maximum of four neighboring elements (two in           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| this example). Unconnected I/O lines are available to external devices. $\ . \ .$  | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

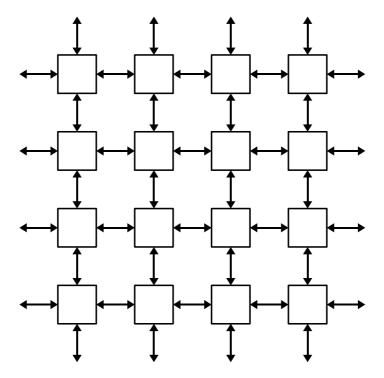

| A $4 \times 4$ set of elements. This collection could be made by connecting four   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| copies of the circuit shown in Figure 2.1 along their edges. Each $2\times 2$ sub- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| collection is, in fact, identical to the circuit shown in Figure 2.1               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

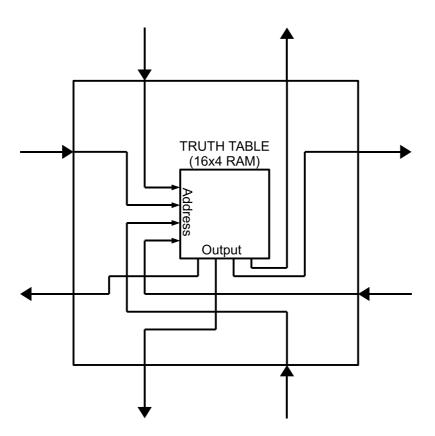

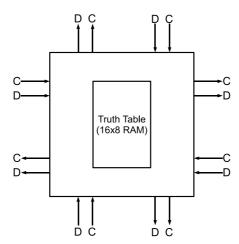

| A single four-sided reconfigurable element based on a 4-input 4-output truth       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| table. The truth table is simply a 16x4 RAM that stores, for each possible         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| combination of the element's four inputs, the precise set of four outputs to       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| be generated. The element can thus be made to perform any desired static           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| mapping. Functions that can be implemented include: logic gates; 2-1 multi-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| plexers; 1-bit adders; and simply wires for routing data among other elements.     | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                    | this example). Unconnected I/O lines are available to external devices A $4\times4$ set of elements. This collection could be made by connecting four copies of the circuit shown in Figure 2.1 along their edges. Each $2\times2$ subcollection is, in fact, identical to the circuit shown in Figure 2.1 A single four-sided reconfigurable element based on a 4-input 4-output truth table. The truth table is simply a 16x4 RAM that stores, for each possible combination of the element's four inputs, the precise set of four outputs to be generated. The element can thus be made to perform any desired static |

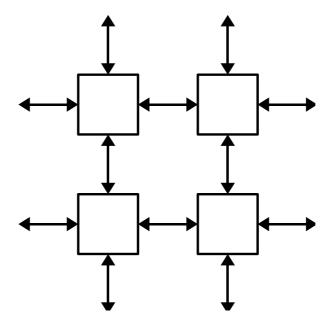

2.1~ A  $2\times2$  set of elements, networked in a nearest-neighbor topology. Each

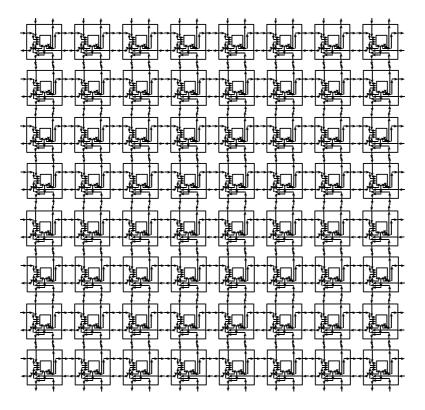

| 2.4 | Collection of reconfigurable elements such as the one shown in Figure 2.3.          |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | By configuring each element to be a particular logic element, piece of a wire,      |    |

|     | or small-scale function, complete digital circuits can be implemented on this       |    |

|     | collection                                                                          | 27 |

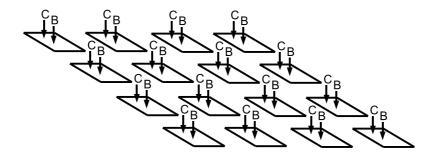

| 2.5 | Reconfigurable elements augmented with configuration inputs. The C input            |    |

|     | is asserted to initiate a configuration operation on the given element. The         |    |

|     | B input is used to send in the new truth table bits, as a serial bit-stream.        |    |

|     | A system-wide external clock is assumed. This figure illustrates a $4 \times 4$ set |    |

|     | of such elements. For clarity, connections between each element and its four        |    |

|     | immediate neighbors are not shown                                                   | 29 |

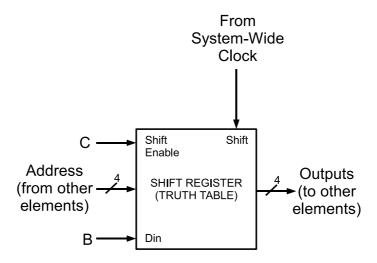

| 2.6 | One possible implementation of a configurable element. The shift register           |    |

|     | stores the cell's truth table, which is loaded by asserting the C input, and        |    |

|     | then sending the desired bit pattern into the B input (synchronized with the        |    |

|     | system-wide clock). The register also needs to be able to act as a 16x4 RAM.        | 31 |

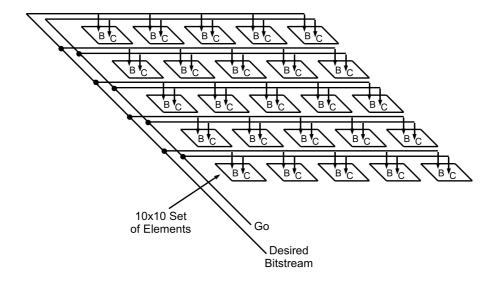

| 2.7 | Sample Bootstrap Circuit. Each square is a $10 \times 10$ set of reconfigurable     |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | elements. The goal is to configure each $10 \times 10$ set identically. The B and   |    |

|     | C inputs are used to load a serial bit-stream that contains 100 truth tables        |    |

|     | (one per each element in the set). Since B and C are shared by all 25 sets, a       |    |

|     | single transmission of the Go and Desired Bit-stream signals will configure all     |    |

|     | sets simultaneously. This is one example of a sometimes useful configuration        |    |

|     | circuit. Omitted from the figure is the circuitry inside each $10 \times 10$ set of |    |

|     | elements that is responsible for distributing the bit-stream to each of its 100     |    |

|     | elements                                                                            | 33 |

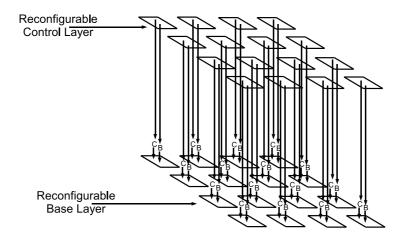

| 2.8 | Reconfigurable Control Layer for Managing the Reconfigurable Base Layer.            |    |

|     | The control layer is composed of a series of identical reconfigurable elements,     |    |

|     | each connected to its immediate neighbors in the control layer plane (for           |    |

|     | simplicity, the connections among elements within each plane are not shown).        |    |

|     | The control layer is able to assert a pair of outputs — B and C — that are          |    |

|     | connected to the B and C inputs of a corresponding base layer element. The          |    |

|     | control layer can be used to build arbitrary digital circuits that manage the       |    |

|     |                                                                                     |    |

36

| 2.9  | Modified Reconfigurable Element. This element is now able to control any           |    |

|------|------------------------------------------------------------------------------------|----|

|      | neighboring element's C and B inputs in order to configure that neighboring        |    |

|      | element. The B input is actually shared with the D input: the meaning of           |    |

|      | the D input is determined by the value of the corresponding C input. The           |    |

|      | truth table still has 16 rows (one for each of the possible combinations of 4 D $$ |    |

|      | inputs), but its width is now 8 bits (4 D outputs and 4 C output)                  | 46 |

| 2.10 | Sample 128 Bit Truth Table. Inputs and outputs have been labeled with              |    |

|      | compass directions ("N," "S," "W" and "E") to indicate which neighbor they         |    |

|      | are connected to. For each combination of D inputs, 8 outputs are specified.       |    |

|      | The collection of 128 outputs bits (b0–b127) constitute the complete identity      |    |

|      | of an element. Not all 128 outputs are explicitly shown in this figure             | 48 |

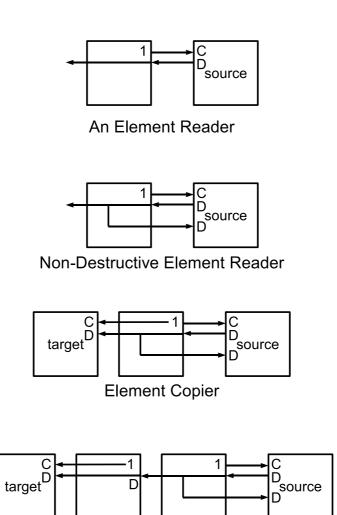

| 2.11 | Circuits for Reading Elements. The basic two-element circuit at the top places     |    |

|      | a source element (on the right) into C mode, reads its truth table, and sends it   |    |

|      | out its western edge. The truth table is replaced with 0s. The non-destructive     |    |

|      | element reader improves on this design by restoring the truth table as it is read  |    |

|      | from the source element. The element copier sends the source's truth table         |    |

|      | bits into an adjacent element that is has also placed into C mode. The source's    |    |

|      | truth table is thus replicated inside the target element, thereby creating a copy  |    |

|      | of the source. The remote element copier extends this circuit further, but using   |    |

|      | an intervening element to route the truth table bits to a non-adjacent target      |    |

|      | element                                                                            | 51 |

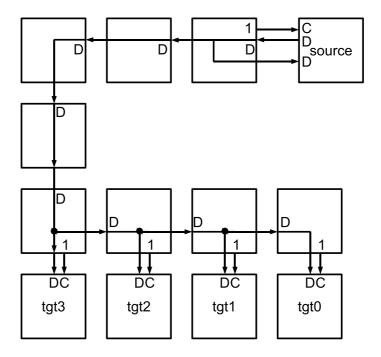

| 2.12 | A parallel replication circuit. The source element's truth table is read, sent   |    |

|------|----------------------------------------------------------------------------------|----|

|      | to the west, then to the south, and then distributed to the east to four ele-    |    |

|      | ments, each located directly above a target element (labeled "tgt0"-"tgt3").     |    |

|      | Each target element is placed in C mode by the element above it. Whatever        |    |

|      | truth table is located in the source element will be copied into the four tar-   |    |

|      | get element. Moreover, this replication occurs in parallel, with all four target |    |

|      | elements being configured at the same time                                       | 52 |

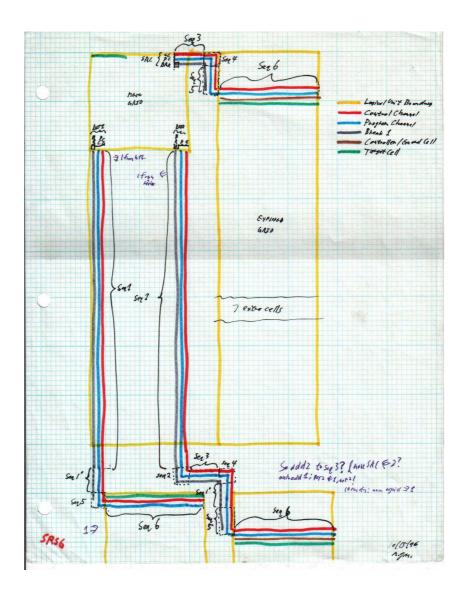

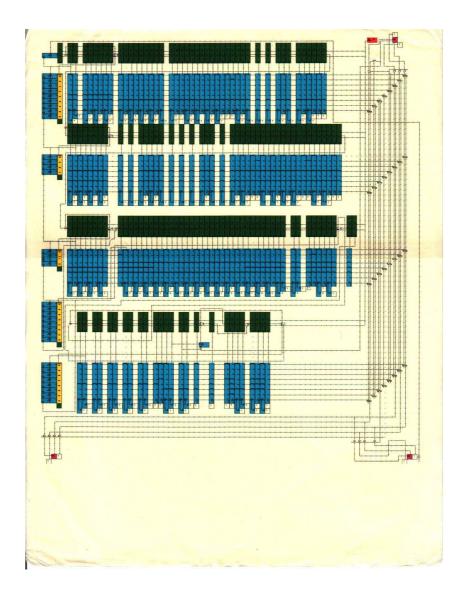

| 2.13 | Sketch of a self-replicating circuit. The main grid (in the upper-left corner)   |    |

|      | reads a copy of itself stored in the exploded grid (right side of the figure).   |    |

|      | The exploded grid is very similar to the main grid, except that there is space   |    |

|      | between each row of elements, and certain elements are prevented from exe-       |    |

|      | cuting by the use of special control elements. The information that's read is    |    |

|      | used to create, to the south, two copies of the main grid: one that is an exact  |    |

|      | copy, and another that is an exploded copy. In this figure, the main grid has    |    |

|      | already begun making copies to the south. When it finishes, there will be an     |    |

|      | identical copy of the original circuit to the south                              | 53 |

| 2.14 | Detailed layout of the main grid of the self-replicating circuit shown in Figure |    |

|      | 2.13. Each small square represents a single element. This main circuit is        |    |

|      | comprised of $85 \times 75$ elements                                             | 55 |

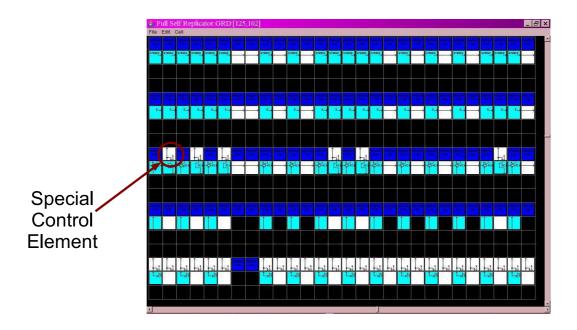

| 2.15 | Blowup of part of the exploded grid. The first row consists of elements that        |    |

|------|-------------------------------------------------------------------------------------|----|

|      | read the source elements in the second row. These source elements correspond        |    |

|      | to the first row of the main grid. The third and fourth rows consist of initially-  |    |

|      | unused elements. These will be used to build wires so that the main grid can        |    |

|      | read the truth table from the source elements in the exploded grid. This            |    |

|      | four-row pattern repeats, and stores the second row of the main grid. Special       |    |

|      | readers can be seen in the $9^{th}$ row: these are special control elements that    |    |

|      | prevent their source element from potentially configuring nearby elements           | 56 |

|      |                                                                                     |    |

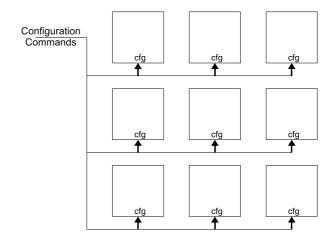

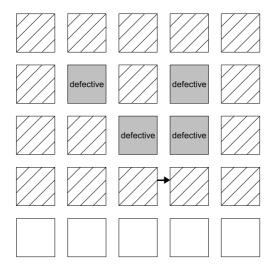

| 3.1  | General Scheme for Parallel Configuration. A single set of configuration com-       |    |

|      | mands are sent to multiple configuration control blocks, to cause multiple          |    |

|      | regions of the device to be configured simultaneously. This results in a device     |    |

|      | configuration that consists of a single pattern, repeated throughout the device     |    |

|      | (in a $3 \times 3$ pattern in this case)                                            | 61 |

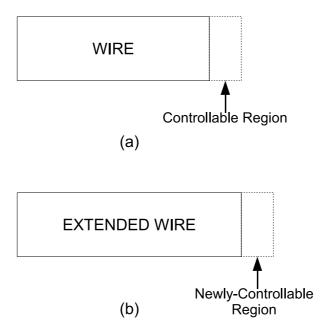

| 3.2  | Simple Extensible Wire. In (a) the circuit ("wire") is able to configure cells to   |    |

|      | its immediate right (within the dashed region). In (b), the wire has configured     |    |

|      | those cells to extend itself, giving itself control over cells further to the right |    |

|      | (within the dashed region). The wire can continue to extend its reach further       |    |

|      | by repeating this process                                                           | 66 |

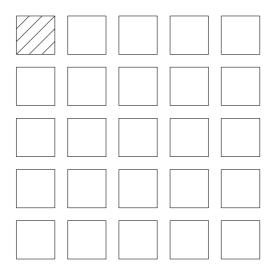

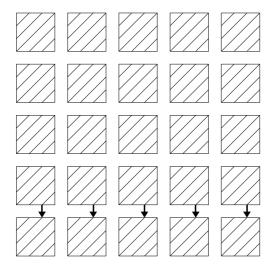

| 3.3  | Initial Medusa Block, shown hatched in the upper-left corner. From this initial     |    |

|      | "seed" the much larger PCS can be efficiently built                                 | 68 |

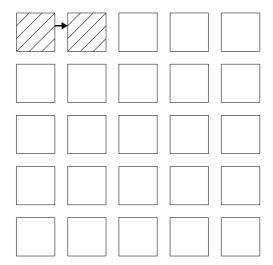

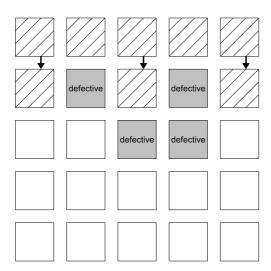

| 3.4  | Second step of PCS Synthesis: the initial Medusa Block has extended, effec-       |    |

|------|-----------------------------------------------------------------------------------|----|

|      | tively adding a second block to the east                                          | 69 |

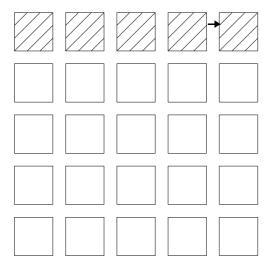

| 3.5  | After a number of steps, the initial seed has extended across a larger region     |    |

|      | of the substrate                                                                  | 70 |

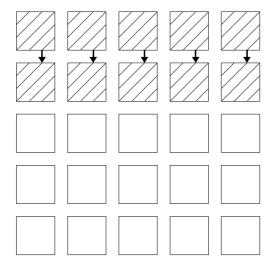

| 3.6  | The initial row of Medusa Blocks has extended one row to the south. Syn-          |    |

|      | thesizing this entire second row requires only a single set of operation: each    |    |

|      | block in the second row is configured in parallel with the other blocks           | 71 |

| 3.7  | Final tiling of the substrate with Medusa Blocks. Each row required only a        |    |

|      | single set of operations to configure                                             | 72 |

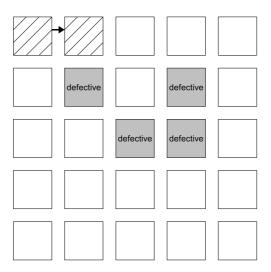

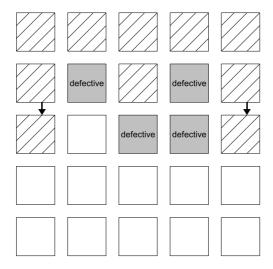

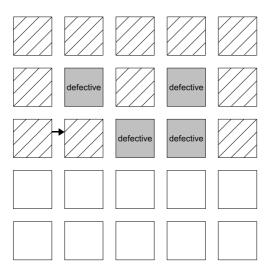

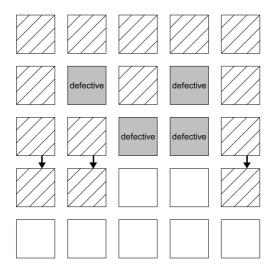

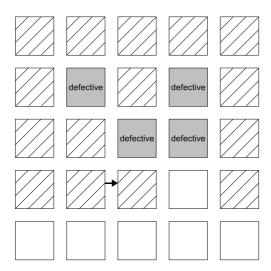

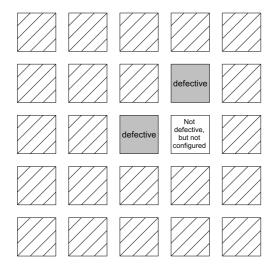

| 3.8  | Initial seed for synthesis of PCS (in upper-left corner). Grayed-out regions      |    |

|      | contain defects, and cannot be used in the synthesis                              | 76 |

| 3.9  | The initial seed has configured one block to its right                            | 77 |

| 3.10 | Eventually, there will be one entire row of configured blocks                     | 77 |

| 3.11 | Since no more progress can be made to the east, the next step is a single         |    |

|      | sequence of configurations to the south                                           | 78 |

| 3.12 | Next the system attempts to configure blocks to the east; but this will fail,     |    |

|      | since all eastern edges are either adjacent to defective regions, or at the east- |    |

|      | ernmost edge of the substrate. The system thus proceeds to configure to the       |    |

|      | south                                                                             | 70 |

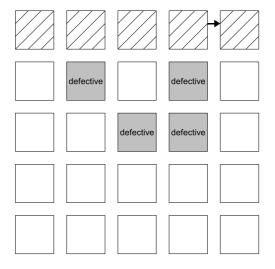

| 3.13 | Configuration resumes to the east, this time creating one new block             | 80 |

|------|---------------------------------------------------------------------------------|----|

| 3.14 | Configuration to the south creates three new blocks. For now, the "shadow"      |    |

|      | of two defective regions has created a hole in the tiling                       | 81 |

| 3.15 | Configuration to the east fills in one of the missing blocks                    | 82 |

| 3.16 | A second configuration to the east fills in the remaining hole. Subsequent      |    |

|      | configurations to the east will fail, so the system again proceeds to perform a |    |

|      | southern configuration                                                          | 83 |

| 3.17 | Following the southern configuration, the entire substrate has been tiled. The  |    |

|      | system will attempt to configure again to the east, and that will fail. It will |    |

|      | then attempt to configure to the south, and that will also fail. It is through  |    |

|      | the presence of this latter failure that the system knows the configuration     |    |

|      | process is complete                                                             | 84 |

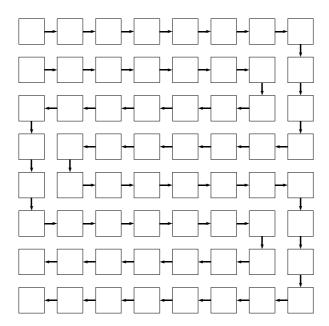

| 3.18 | Movie showing parallel configuration of an array containing defects. Click on   |    |

|      | the figure to launch the movie player.                                          | 86 |

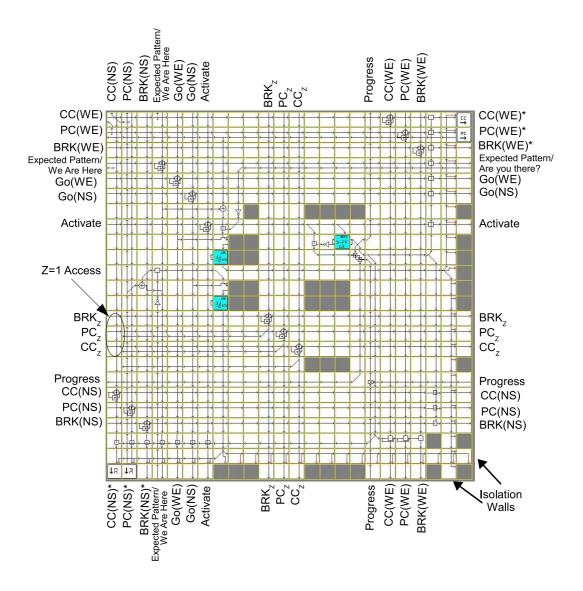

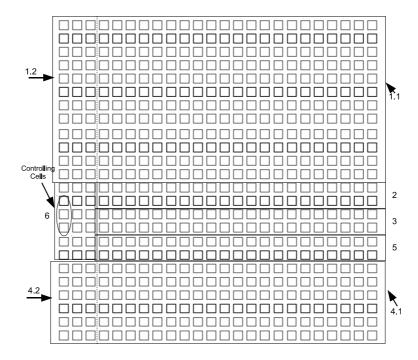

| 3.19 | $24 \times 24$ Medusa Block. Most signals are transmitted from the north and west |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | to the south and east (ORed inside the block). CC, PC and BRK are wire            |     |

|      | extension commands: CC(WE) is for a west-to-east extension, and so on.            |     |

|      | Signals marked with a "*" ( $CC(WE)$ * on the east for example) are "live,"       |     |

|      | meaning they can configure cells within adjacent unconfigured blocks. Other       |     |

|      | signals (CC(WE) on the south, for example) are pure data, and will never          |     |

|      | configure adjacent cells                                                          | 88  |

| 3.20 | A particularly bad arrangement of defects. The region shadowed by both            |     |

|      | defects will not be configured, even though it contains no defective cells        | 91  |

| 3.21 | Serpentine extension pattern for testing a region of cells. The basic extensible  |     |

|      | wire is two cells in height, and extends initially from the upper-left corner to  |     |

|      | the east. When it nears the eastern edge, it makes two clockwise turns, and       |     |

|      | then extends to the west. At the western edge, it makes two counterclockwise      |     |

|      | turns, and continues again to the east. This pattern repeats until the entire     |     |

|      | region has been filled by this single extensible wire. Testing of cells occurs    |     |

|      | during this extension                                                             | 97  |

| 3.22 | Movie showing detection of defective elements. Click on the figure to launch      |     |

|      | the movie player                                                                  | 101 |

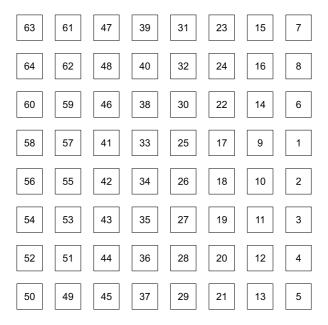

| 3.23 | Order of cell configuration for an $8 \times 8$ region of cells. beginning in the upper- |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | left corner, a wire is built across the top of the region; turned clockwise; and         |     |

|      | extended from top to bottom. During this extension, regions to the right                 |     |

|      | of the wire's head are configured as desired. Thus, the configuration order              |     |

|      | is generally from top to bottom, and from right to left (row-major, column-              |     |

|      | minor). Because the wire used to configure this region is itself three cells wide,       |     |

|      | the top three rows require a different configuration order, as do the leftmost           |     |

|      | two columns. This particular order ensures that new cells can be configured              |     |

|      | without disturbing already-configured cells. The procedure is similar to how             |     |

|      | one might paint the floor of a room while leaving the paint can in a fixed               |     |

|      | location near one corner                                                                 | 106 |

| 3.24 | Order of cell configuration for a 24 $\times$ 24 region of cells at $Z=1$ . because      |     |

|      | configuration is being driven from midway along one edge, the configuration              |     |

|      | order is more complicated than as in Figure 3.23. First the upper part of the            |     |

|      | region is configured in a normal way. Then two of three thin bands between               |     |

|      | the upper and lower regions are configured. The lower region is configured               |     |

|      | next, followed by the thin band in-line with the driving cells. Configuration of         |     |

|      | a small number of remaining cells in the vicinity of the driving cells completes         |     |

|      | the configuration of the entire region                                                   | 109 |

| 3.25 | Movie showing 3–D parallel configuration. Click on the figure to launch the              |     |

|      | movie player                                                                             | 110 |

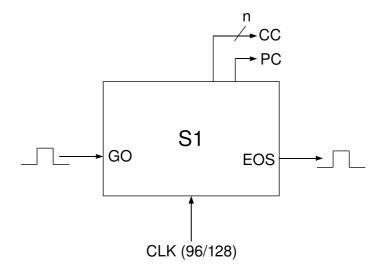

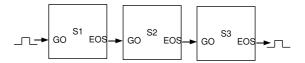

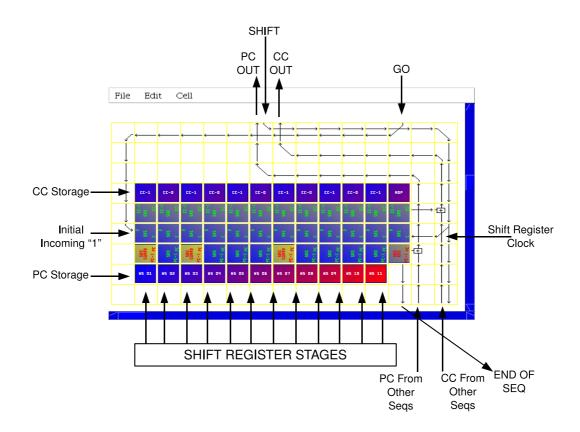

| 4.1 | Single-Sequence Generator Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 117 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

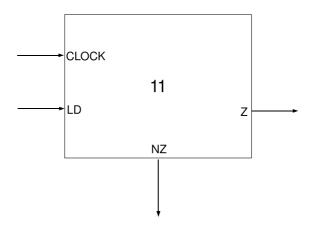

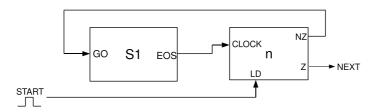

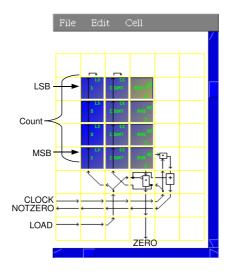

| 4.2 | Counter Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 118 |

| 4.3 | Three-Sequence Supersequence Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 119 |

| 4.4 | Circuit for Generating Multiple Iterations of Sequence S1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 121 |

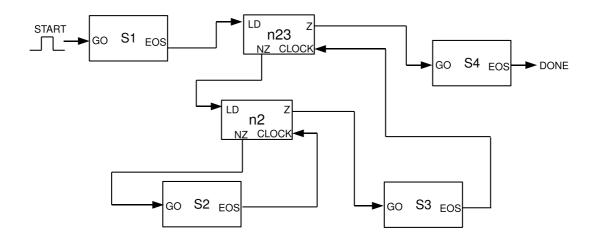

| 4.5 | More-Complex Supersequence Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 123 |

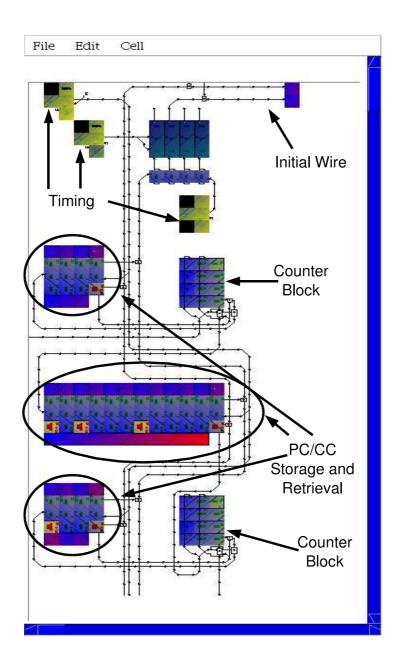

| 4.6 | Complete Supersequence Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 125 |

| 4.7 | PC and CC Storage and Retrieval Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 126 |

| 4.8 | Sequence Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 130 |

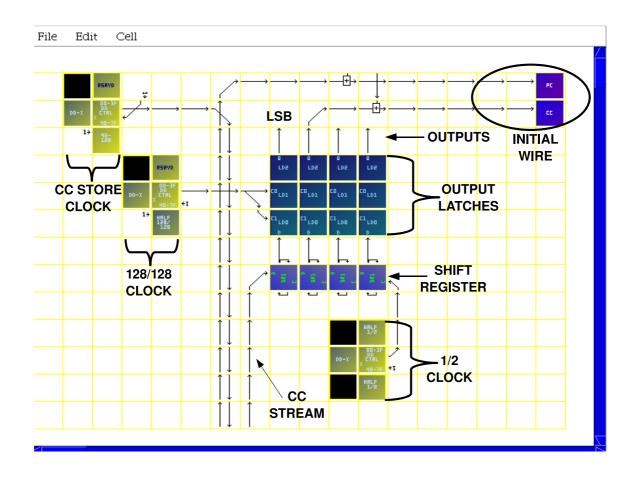

| 4.9 | CC Shifter, Timing Control and Initial Wire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 133 |

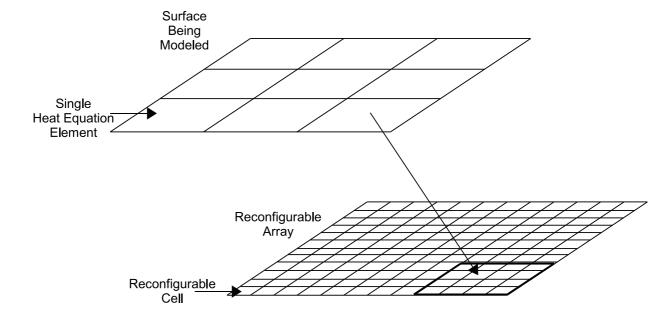

| 5.1 | Modeling of Heat Flow across a 2-D Surface. The surface being modeled is divided into a number of elements, each of which will be treated as having a uniform temperature across its entire surface. The PDEs that describe thermal flow are approximated by difference equations, and each element's thermal flow is modeled on a series of reconfigurable cells in an underlying reconfigurable substrate. In this example, the tiling of the surface is uniform, but in practice an <i>irregular mesh</i> might be used to more-accurately model the |     |

|     | system where surface variation is higher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 140 |

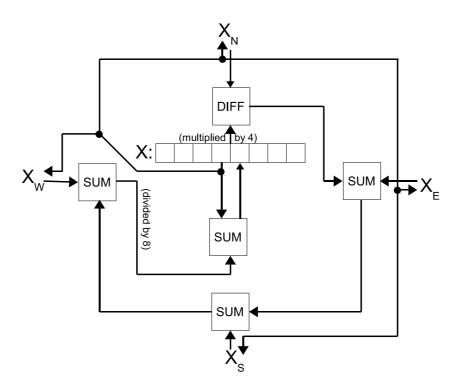

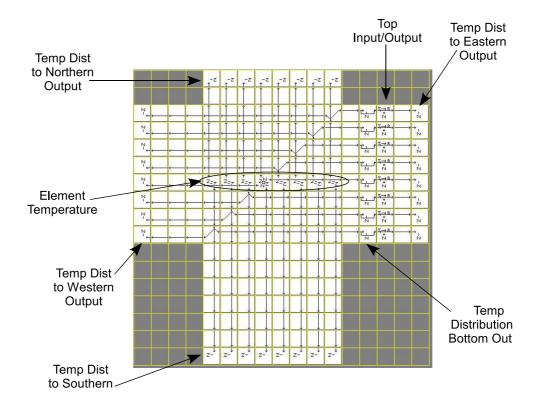

5.2 Block Diagram of a 2-D Heat Equation Solver. A number of these elements are tiled in a 2-D array, with each internal element connected to four neighboring elements. Temperature is represented as an 8-bit signed integer, and is stored inside each element in the register labeled "X." Each element sends its own temperature to its neighboring elements, and receives each neighbor's temperature through an input along its perimeter (elements along the edge of the tiled array read boundary conditions from one or more of their inputs). X is multiplied by 4 (via a simple 2-bit left shift); the four input  $(X_N, X_S, X_W)$ and  $X_E$ ) are summed, and 4x is subtracted from that sum. The difference is divided by 8 (right-shifted 3 bits): this corresponds to scaling the difference by a thermal coefficient  $\alpha = 0.125$ . The scaled difference is added to X to compute the element's temperature at the next time step. X is stored in a master/slave flipflop, so that changes to its input are latched before the output changes. This allows all elements to update their temperature simultaneously

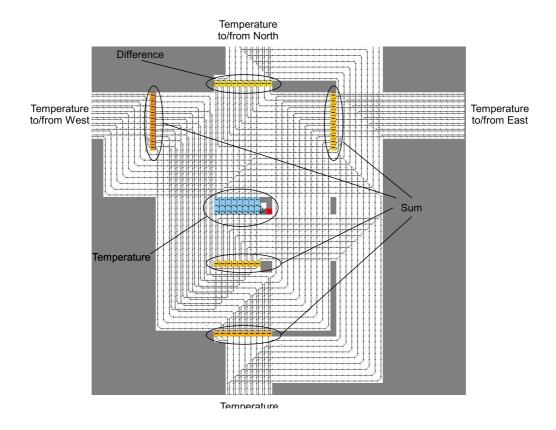

| 5.3 | Cell-Level Implementation of a Single Heat Equation Element. The element's       |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | temperature is stored in the register in the middle of the circuit, and is sent  |     |

|     | to each of the element's neighbors (on the north, south, west and east. The      |     |

|     | Temperature is shifted left 2 bits, of produce $4 \times Temperature$ , which is |     |

|     | subtracted from the temperature received from the north. To this difference      |     |

|     | is added the temperatures from the east, south and west. This final sub is       |     |

|     | shifted right 3 bits, and added to the current temperature. The final result     |     |

|     | is loaded into the Temperature register on the rising edge of its clock input.   |     |

|     | On the falling edge of the clock input, the register's outputs are changed to    |     |

|     | reflect the latched input                                                        | 145 |

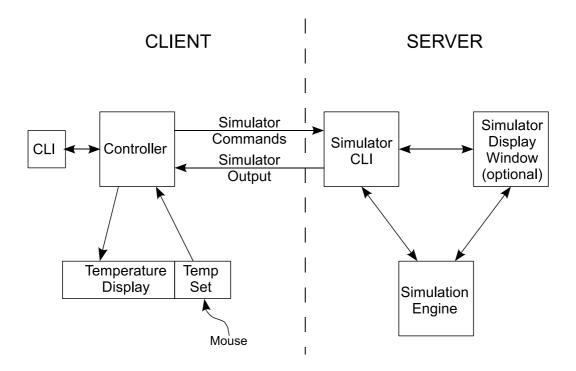

5.4

| 5.5 | Movie showing behavior of heat-flow-simulation circuitry. Click on the figure   |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | to launch the movie player                                                      | 150 |

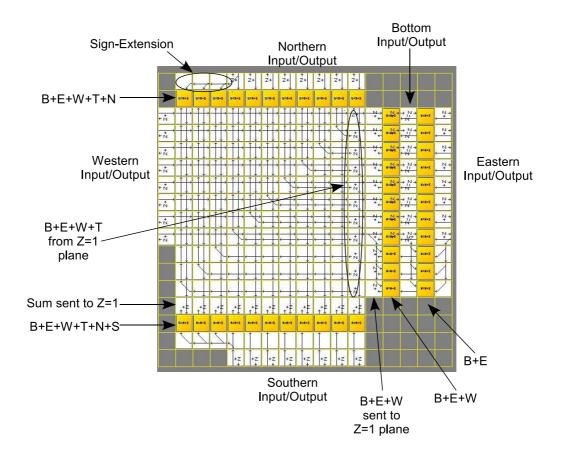

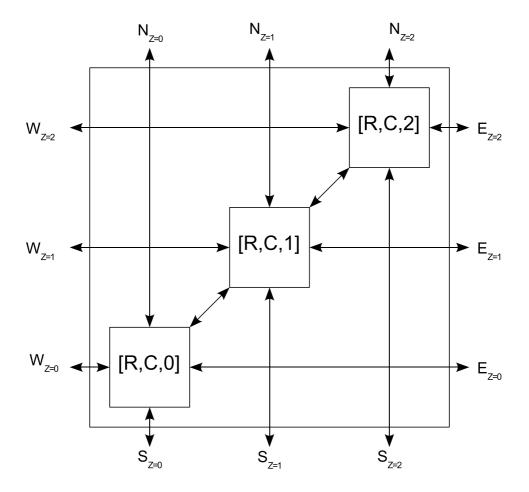

| 5.6 | Z=0 Plane of 3-D Heat Equation Element. Temperature readings from the           |     |

|     | north, south, west, east, top and bottom elements are designated "N," "S,"      |     |

|     | "W," "E," "T" and "B" respectively. I/O with neighbors uses 8-bit integers,     |     |

|     | which are sign-extended to 11 bits internally (to prevent overflow). This plane |     |

|     | mainly calculates the sum of the temperature from all neighbors (part of the    |     |

|     | calculation is performed on the $Z=1$ plane). The final sum is sent to the      |     |

|     | Z=1 plane for further processing                                                | 154 |

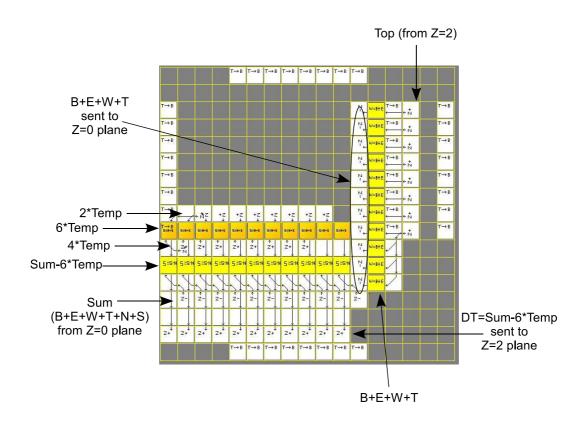

| 5.7 | Z=1 Plane of 3-D Heat Equation Element. This plane subtracts $6 \times Temp$    |     |

|     | from $B+E+W+T+N+S$ to compute the element's change in temperature               |     |

|     | DT. $DT$ is passed to the $Z=2$ plane for further processing                    | 155 |

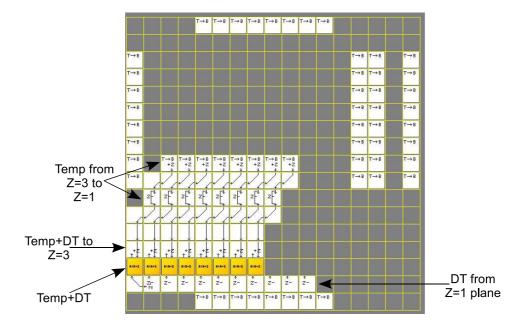

| 5.8 | Z=2 Plane of 3-D Heat Equation Element. This plane helps compute 6 $\times$     |     |

|     | Temp, and also computes the element's new temperature= $Temp + DT$              | 156 |

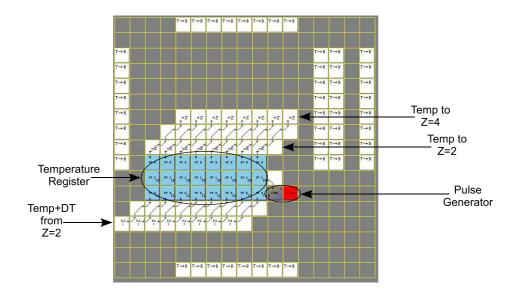

| 5.9 | Z=3 Plane of 3-D Heat Equation Element. This plane contains the register        |     |

|     | that stores the element's temperature, as well as the update circuitry for      |     |

|     | loading the element's new temperature at each time step. The Pulse Generator    |     |

|     | generates a pattern of 1s and 0s that are fed to the register's clock input.    |     |

|     | Each uptick/downtick pair of pulses on the clock input causes the register to   |     |

|     | be updated with the element's new temperature                                   | 158 |

| 5.10 | Z=4 Plane of 3-D Heat Equation Element. This plane communicates with                                    |     |

|------|---------------------------------------------------------------------------------------------------------|-----|

|      | the 5-plane element directly above it. It also distributes the element's own                            |     |

|      | temperature to the edges of the plane, where it is passed down to lower planes,                         |     |

|      | until it reaches the $Z=0$ plane, that sends the temperature to its neighbors.                          | 159 |

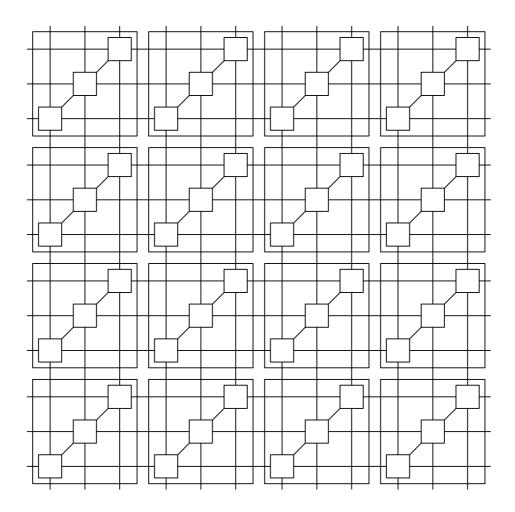

| 5.11 | A single $1 \times 1 \times 3$ element that can be scaled in the $X-Y$ plane to produce                 |     |

|      | an arbitrarily-large $X \times Y \times 3$ 3-D array. Note that all three planes are                    |     |

|      | physically co-planar, but are wired together as independent planes                                      | 162 |

| 5.12 | $4 \times 4 \times 3$ array of cells, comprised of a regular tiling of a scalable $1 \times 1 \times 3$ |     |

|      | sub-array. Note that if four of these arrays are tiled in X and Y, the result                           |     |

|      | will be a large $8 \times 8 \times 3$ array. However, there is no way to connect these                  |     |

|      | elements so as to produce a circuit containing more than three planes. To do                            |     |

|      | so, internal connections much be rewired                                                                | 163 |

### Chapter 1

### Introduction

"Size matters not" [?]. So proclaims Yoda, the mythical Jedi Knight from the Star Wars series. Admittedly, that utterance was made a long time ago, in a galaxy far from Silicon Valley. But in 2011 in Silicon Valley, size definitely matters. The semiconductor industry is absolutely obsessed with the size of transistors. For several decades, devices have gotten smaller and smaller. This trend is not simply some side-effect, but is one of the primary driving forces behind innovation in the industry. It is so ingrained in the collective psyche that an observed trend — the doubling of the number of transistors per integrated circuit every two years — has been dubbed a "law" [?]. Continued reduction in transistor size forms a key part of the semiconductor industry's ITRS (International Technology Roadmap for Semiconductors) [?] — the supposed guide of the path that must be followed for future prosperity. Foundries are often identified by a single characteristic of their output: the gatewidth of manufactured transistors. Mention of a new foundry start with a smaller feature

size in a corporation's 10-K filing is certain to fuel investor confidence for another quarter. By multiple measures, the semiconductor industry is seriously invested in maintaining this trend of ever-decreasing transistor size, and with good reason: this continued reduction in transistor size has helped foster tremendous growth in the industry, and in industries that rely on semiconductor technology.

While transistors have continually shrunk in size over the past several decades, the integrated circuits containing those transistors have generally stayed the same size. This leads to the most noticeable effect of this ongoing reduction in transistor size: an increase in the number of transistors per fabricated device — again, Gordon Moore's observation. In the area of CPU design, this continual increase in transistor count has manifested itself in several different architectural aspects, including wider datapaths, more-advanced floating point capability, larger on-chip caches, and the inclusion of advanced architectural features such as branch prediction. This ongoing increase in the power of computing devices has influenced almost all aspects of modern life, including areas such as communications, networking, transportation, energy and medicine. By most measures, this would certainly be considered a highly-desirable state of affairs.

But there is a storm coming — a dark cloud nestled inside the silver lining of lithographic innovation. Its arrival is inevitable, for it is directly tied to the very thing the industry craves: the ever-increasing density of fabricated devices. This increase in density and transistor count is certainly advantageous in many ways. However, as the number of transistors increases, several technical problems grow more severe.

- The design time for systems utilizing a large number of transistors grows much more than linearly with the device count.

- As designs grow more-complex, design cost is also ever-increasing, including the over-head of managing ever-larger design teams. Other NRE (non-recurring engineering) charges also continue to increase.

- The cost of building a new chip foundry is roughly doubling every 2–3 years. This is Moore's Second Law [?].

- As gate-widths continue to shrink (along with other fabricated features such as metal lines), the defect rate in fabricated devices continues to rise, with yields dropping accordingly.

- As switching voltages drop and clock frequencies rise, the likelihood of upsets in transistor outputs increases, and the mean time between failures (MTBF) drops.

- The number of I/O pins per packaged device has grown very modestly compared to the number of transistors. Thus the number of transistors per I/O pin is growing rapidly.

Put differently, the I/O bandwidth available per transistor is continuing to shrink.

- The combination of faster switching times, smaller wires with higher resistance, and increased transistor density means that heat generation within a chip continues to increase.

As clock frequencies increase and clock lines are distributed to more and more transistors, clock skew becomes a bigger problem.

These are some of the challenges currently faced by designers and manufacturers of integrated circuits. Each time feature sizes drop, these problems grow a little more severe. So far though, these reductions in feature size have occurred relatively infrequently — every couple of years. This gives the industry time to make incremental improvements, for example, in the design process, in manufacturing capabilities, and in ways to mitigate or handle faults and defects. In this sense, the fact that development is not occurring more-quickly is actually advantageous to the industry.

This situation may soon change though. While there is concern that Moore's law may one day end, in the sense that progress may falter, there is another possible scenario: the end of Moore's law because of a sudden, dramatic *increase* in device density. Such a hypothetical event has sometimes been called *The Singularity* [?]. This dramatic increase may come about from a combination of several factors, including:

- the development of a fundamentally new, highly-scalable switching technology to replace the transistor [?];

- developments in quantum computing [?];

- development of fabrication techniques that allow physically-larger devices to be manufactured (i.e., wafer-scale integration [?]);

- the advent of our ability to perform true atomic-scale manipulation of matter (as proposed by Richard Feynman in 1959) [?]); and

- a transition from fundamentally flat fabrication to the creation of full three-dimensional structures (as opposed to two-dimensional structures with a small amount of height in the Z axis) [?].

At such a point, the industry for creating computing circuits may resemble chemistry more than electronics.

In chemistry, a common unit of measure is a mole, defined as "the amount of substance of a system that contains as many elementary entities (e.g. atoms, molecules, ions, electrons) as there are atoms in 12 g of carbon-12 (12C)" [?]. At the point when circuits are built by placing individual atoms, it may make sense to discuss a "mole of switches," i.e., a circuit containing approximately  $6.02 \times 10^{23}$  transistors (or transistor-like switches). Such a system would be over fourteen orders of magnitude more complex than today's most-advanced computing devices.

Supposing such a singularity does occur — and it's certainly a good possibility, given the growing interest in such breakthroughs, and the development of facilities and programs to support such research, e.g. Ray Kurzweil's "Singularity University" [?] — what will the chipdesign landscape look like? Considering the above complicating-factors, given an increase in complexity of more than a trillion times, one might predict the following trends:

• design time and design cost will each increase to the point of being infeasible;

- defect rates will make fabrication of perfect devices extremely difficult;

- the ratio of transistors to I/O pins will become huge, leading to a continuation of the long-standing problem of I/O bandwidth; and

- total system-wide heat generation will increase dramatically [?, ?].

One might also expect a number of other formidable technical challenges, including the development of fundamentally new design tools.

The real challenge here is that the present way of doing things — the basic architecture of systems, the way those systems are designed, the way they are manufactured, and how they behave at runtime — simply does not scale very well. With much work, the industry can almost keep pace with a bi-annual doubling in transistor count. But it's unlikely that present methodologies will scale well in response to something like a sudden, one hundred trillion times increase in switch density. Part of the difficulty lies in the basic assumptions about how to design next-generation devices:

- an expectation of fabrication to produce perfect, defect-free chips;

- a hope to ramp up clock speed despite its effect on heat generation and problematic clock skew;

- the use of packages with a relatively small number of pins, and reliance on those few pins to monitor and control an ever-increasing number of transistors inside the fabricated chips;

- the use of a basic system architecture the Von Neumann stored-program CPU/memory architecture that is several decades old;

- the building of new foundries whenever physicists find a way to do fabrication at a smaller scale; and

- a practice of completely re-designing the systems being built each time the device density increases.

A different approach is needed — a different way of doing things:

- The design of systems needs to be changed, to something more-scalable, something that does not need to be re-designed when there are more switches available. This probably means something composed of many homogeneous elements, where it's possible to simply "add more elements" and end up with a larger, more-powerful system. It also suggests a fairly simple interconnection scheme among those elements.

- The manner in which systems are designed needs to change. Having teams of people designing systems by hand, and using single-CPU or modestly-parallel workstations to compile those designs, is simply not going to be practical. A better approach might be to create systems that are able to design themselves, perhaps using their own massive parallelism to effect more-efficient place-and-route, etc.

- The ever-decreasing bandwidth of I/O subsystems needs to be dealt with, by finding ways to manage complex systems from within those systems themselves, instead of

trying to control them through a relatively small number of macroscopic I/O pins.

- The way in which speed is extracted needs to be changed achieving speedups through massive parallelism vs. ever-increasing clock frequency.

- The way in which defects and runtime faults are viewed needs to change accepting them as an inevitability and learning how to function in their presence, instead of assuming they can be ignored.

So how can system architecture, complex circuit design, and run-time behavior be re-thought given the above considerations? The proposed answers discussed herein are based on four observations/hypotheses about industry trends.

### 1.1 Hypothesis about future computing

Hypothesis 1: Industry trends point to a continuing shift towards extremely large reconfigurable devices.

Two primary trends in the industry are working fundamentally against each other. This first trend — ever-increasing density and transistor count — suggests that devices will continue to grow more complex over time. The second trend — increasing costs associated with this growth — suggests that custom ASIC is becoming unaffordable to all but the largest entities (those that can amortize NRE costs across a huge volume). The combination of these trends thus suggests a continuing move to reconfigurable devices: hardware that has a fixed design,

but can be customized post-manufacture by the user for their specific needs. This is the first hypothesis of this dissertation.

Hypothesis 2: As the number of transistors in reconfigurable devices continues to increase, it will become increasingly useful if those transistors can be monitored and manipulated from inside the device itself.

This is based on consideration of additional trends which further complicate the long-term picture. As switching voltages drop, the likelihood of glitches — momentary changes in the logical value of a signal — increases. As the physical size of transistors shrinks, the probability of a manufacturing defect — a short or open circuit, or a misalignment between masks — also increases, as does the probability of undesirable run-time phenomena such as metal migration. The increased likelihood of these and other failures within the reconfigurable device suggests a growing need for constant monitoring of system behavior. Normally, this monitoring can be done using external circuitry to access different points inside the system. Such monitoring can make extensive use of I/O resources to provide sufficient addressability for probing numerous points inside the system. However, while the number of transistors within a device has grown rapidly, the number of I/O pins available on a package has grown much more slowly. Rent's Rule [?] relates the number of pins P on a device to the number of gates G contained in the device as  $P = tG^q$ , where t and q are constants, and 0 < q < 1. Re-writing this equation, the ratio of gates to pins  $G/P = (1/t)G^{1-q}$ .

This suggests that continued reliance on external systems to analyze and manage the transistors within a device will lead to increasingly long delays as more and more transistors

are accessed from a comparatively small number of I/O lines. To circumvent this problem of limited I/O, one can consider a system design where the monitoring and control of the system's transistors is done, not by external systems, but *from inside the system itself*.

Hypothesis 3: Having the internal management circuitry itself be reconfigurable increases the flexibility and general usefulness of the system. This is because, as the number of reconfigurable elements grows *larger*, the circuitry for managing those elements is also going to grow, and probably become more-complex. And in the same way that an FPGA is sometimes a useful alternative to a fixed custom ASICs, a reconfigurable management system may be more useful than a fixed one. This is simply because decisions about exactly how that system should be designed can be made post-manufacture, and can be changed based on how the reconfigurable elements are going to be configured and used.

Hypothesis 4: If the reconfiguration of management circuitry is indistinguishable from the reconfiguration of target circuits, then you eliminate hierarchy, or in some sense "close the loop" between the top-level and the bottom-level of the hierarchy. This is more subtle than the other hypothesis, and will be covered in more detail in the next chapter. The basic idea is that, if the control/management layer is itself reconfigurable, then what will control that layer's configuration? If R is the set of reconfigurable elements, and  $C_1$  is the control layer for R, and  $C_1$  is reconfigurable, the there must be a control later  $C_2$  for controlling  $C_1$ . And while  $C_2$  can be fixed/hardwired, the issue is, as R grows, the size and complexity of  $C_1$  will also grow, and thus so will  $C_2$ . If R gets large enough,  $C_2$ 's size and complexity may become large enough that having  $C_2$

itself be reconfigurable may be desirable, leading to the inclusion of yet another control layer  $C_3$ , and so on. One way to break this chain of ever-deeper layering of control systems is to simply allow  $C_1$  to configure itself, i.e., to play the role of  $C_2$ ,  $C_3$ , and so on. An even simpler solution is to allow R to be its own stack of control layers  $\{C_n\}$ . This is the essence of Hypothesis 4: to have the set of reconfigurable elements and the set of reconfiguring elements be indistinguishable from each other, because they are exactly the same set of elements.

### 1.2 Prior Art

The basic architecture discussed herein has been previously explored, under the name "Cell Matrix" [?, ?, ?]. While the Cell Matrix is a useful instance of a particular self-configurable architecture, the concepts developed in this work are meant to be largely independent of any particular self-configurable, hierarchy-free architecture. The present work, however, does extend prior Cell Matrix research in a number of ways, including the development of new tools, new circuits and sequences, and new methodologies for internally-directed creation of circuitry.

#### 1.3 Bio-Inspiration

Much of this work, including the background work in the Cell Matrix, derives from ideas found in biology. General concepts such as using the parallelism of a large number of slow,

simple processors to perform powerful computations (vs. relying on a single complex, extremely fast CPU) have obvious analogues in natural systems. Similarly, the idea of reducing critical areas in a system, i.e., minimizing the number of points where a single failure will render the entire system inoperable, is found in many biological systems. While the present work does not seek to *mimic* nature, it does draw from examples in nature for motivation and ideas for new directions in which to explore.

Moreover, there are directions in which this work could be taken that derive more-directly from biology, such as in implementation of neural networks, or the development of embry-ological circuitry. While such directions would most-likely prove to be fruitful, the present work is not focused on such applications, but rather on an analysis of the underlying concepts of self-configuration, and its usefulness in support of extremely-large reconfigurable systems.

### 1.4 Scope

A number of tools have been developed in the course of this work, but it is important to note that these tools are exploratory in nature, and are primarily intended as a means to an end, namely a deeper understanding of certain concepts related to self-configuring circuitry. This is not a work on tool-development *per se*, and it is not the purpose of this work to expand on present knowledge in tool development, place-and-route techniques, and so on.

### 1.5 Organization of paper

The remainder of this paper is organized as follows:

- Chapter 2 presents an overview of a reconfigurable system that supports internal monitoring and configuration of its reconfigurable elements. While the techniques presented in this paper will be applicable to general systems that support self-configuration, working with a specific reconfigurable architecture will simplify the discussions.

- Chapter 3 discusses one particular application of internal control, for managing the initial configuration of a very large collection of homogeneous sub-circuits. This will also illustrate the usefulness of Hypothesis 4, as the synthesized configuration circuit will be used to synthesize the configuration circuit itself.

- Chapter 4 describes some general techniques for manipulating circuits from inside a reconfigurable device itself. The circuits and *sequences* described will be used throughout much of the remaining work described herein.

- Chapter 5 illustrates a specific application of these techniques: a massively-parallel system for simulating heat flow through a 2-D or 3-D medium, based on the 2-D and 3-D heat equation. This application will map a material being analyzed onto a set of reconfigurable elements. Efficient initial configuration of the system using the concepts presented in Chapter 3 will also be discussed.

- Chapter 6 will collect the results of the previous chapters, and compare them to similarly-sized systems implemented with other potential technologies.

- The paper concludes with Chapter 7, which summarizes the findings and discusses future work.

# Chapter 2

# Background

This chapter discusses architectural considerations related to the four main hypothesis of this paper. To re-iterate, these are:

- 1. Industry trends point to a continuing shift towards extremely large reconfigurable devices;

- 2. As the number of transistors in reconfigurable devices continues to increase, it will become increasingly useful if those transistors can be monitored and manipulated from inside the device itself;

- 3. Having that internal management circuitry itself be reconfigurable gives maximum flexibility; and

4. If the reconfiguration of management circuitry is indistinguishable from the reconfiguration of target circuits, then you eliminate hierarchy, and in some sense "close the loop."

These are fundamentally different from the standard CPU/memory model which utilizes a single (or, in modern cases, perhaps several) processors; is not scalable; and is comprised of fixed hardware. The following sections will discuss each of the above criteria, how they can be achieved, and what the consequences of them are.

### 2.1 Large-Scale Reconfigurable Systems

Traditional computing has long been based on the von Neumann model [?], comprised primarily of two components:

- a memory that stores both data and instructions; and

- a central processing unit (CPU) that performs calculations on the stored data, in accordance with the stored instructions.

While the basic design of a memory may be the same regardless of its capacity, it is generally not possible to simply "add more transistors" to an existing design to create a larger memory. While one can increase the width of the memory (i.e., the number of bits stored at each address), this is generally not as useful as extending the *length* of the memory, i.e., the total number of memory locations that can be addressed. Doing so requires not only a wider

address bus, but a more-complex address-decoding system for selecting the desired memory cells based on the address. The extension of a memory architecture to a larger capacity can be done in a fairly automated way, but it's certainly not as straightforward as simply connecting, say, 1,000 memories together side-by-side to create a larger memory.

Scaling of a CPU is also challenging. While it is possible to design small CPUs specifically to be scalable — as was done, for example, by AMD in their 2900 Family of bit-slice devices [?] — in general a CPU is not a scalable design. Given a pair of four bit processors (such as the Intel 4004), it's not clear how to connect them somehow to produce an 8-bit processor. Equally difficult is imagining how to simply double the number of transistors inside the device to achieve an 8-bit processor. Even by widening the registers, buses, ALU, and so on, one still would need to consider expanded addressing modes, more-sophisticated instruction sets, and so on (a 64-bit processor possessing the 4004's instruction set and addressing modes would probably be of limited usefulness).

This scaling difficulty is somehow inherent in the von Neumann model. This may be because it's based on a single-process; and while, given more transistors, it may be feasible to manufacture "more CPUs," there's no clear way to manufacture "more CPU."

Reconfigurable hardware [?] offers an alternative to the von Neumann CPU/memory model. Each is a general-purpose system, but with a basic difference:

• a CPU/memory system has fixed circuitry; its generality comes from its *programma-bility*, i.e., its ability to execute different algorithms on that fixed circuitry; whereas

• reconfigurable hardware's generality comes from the ability to change the circuitry itself.

At some level, reconfigurable hardware is more-easily scaled up, according to ones ability to design and utilize larger circuits (circuits containing more transistors, gates, etc.). However, there is still an architecture associated with reconfigurable devices: an organization of the "blank hardware" in a way that allows a configuration to be loaded into the system so as to achieve the desired functional behavior.

Of course, for presently-available reconfigurable devices, the lowest-level underlying hardware does not physically change when the device is configured. There is still a static base-layer of hardware, that, in some sense, interprets the desired configuration of the system. For example, a block might be specified to act as an AND or a NOR gate based on the value loaded into a nearby register.

Most modern reconfigurable devices, such as those by Xilinx, are configured by loading a configuration string into the device. This string has a specific (usually per-device-type) organization, and generally specifies the functional behavior of each reconfigurable element in the system, as well as their interconnection with each other.

While it may be straightforward to design a larger circuit (i.e., one that uses more hardware), the design of a larger reconfigurable device is not so straightforward, and designing a device that contains more reconfigurable elements may require re-architecting the entire system. Thus, while hardware designs may be "more scalable," the devices on which these designs

are implemented still do not scale very easily.

If we wish to utilize trillions of transistors (or  $10^{23}$  transistors, as in an Avogadro machine), we need a base architecture that not only supports reconfiguration, but one that also scales up naturally, i.e., one which can utilize an ever-increasing number of available transistors without needing to be fundamentally re-designed.

### 2.1.1 A Scalable Design

For our purposes, a perfectly scalable architecture is one with the property that if two identical systems S are (in some way) connected to each other, the result is a larger version S' of that same system. The way in which this connection occurs may vary; what is important in this definition is that no changes need be made  $inside\ S$  in order to two (or more) of them together. Another way to view this is as follows: if one looks at a subset of S', it will be impossible to tell if one is looking at a section of S', or at the original system S. In some sense, a perfectly scalable architecture thus possesses a fundamentally fractal nature [?]. Devices such as those in the Xilinx Virtex series incorporate a sophisticated, hierarchical routing system for interconnecting configurable elements [?]. While this potentially simplifies generation of a configuration file and improves performance of the implemented circuitry, it is unfortunately an impediment to scaling the system: generally, the more components contained inside the device, the more-complex the routing system will be (there are other impediments to scalability as well, such as the internal configuration mechanism, that will

be discussed below).

Figure 2.1 illustrates an alternative routing system, based on the notion of nearest neighbors. In such a system, each reconfigurable element is connected to a fixed set of neighboring elements, according to an established system-wide topology. Such a scheme satisfies our definition of a perfectly scalable architecture. Of course, there may be factors such as propagation delay, power requirements, and so on that affect how scalable the system is: but from an architectural point of view, no changes are needed in the design in order to create a larger system.

Figure 2.1 shows a set of four elements connected in this planar, nearest-neighbor way. Figure 2.2 shows four such sets, connected along their edges, to form a larger  $(4 \times 4)$  set of elements. The nature of the reconfigurable elements must also be decided. There are many possibilities for what to endow these blocks with: memory, arithmetic units, signal processing subsystems, text processors, or complete CPU/memory systems are all interesting options, and depending on the nature of the problem being solved, each of these may be a good choice. However, since the goal is to architect a single, universal system, a simpler element from which more-

The simplest form of combinatorial processing is a simple map from inputs to outputs, e.g., a truth table. Such a map can consume a large amount of memory: for example, a 10-input 10-output device would require 2<sup>10</sup> rows of memory, each 10 bits wide, for a total of 10,240 bits, assuming one wished to be able to represent **any** possible mapping from inputs to outputs.

complex units may be built will prove most-generally useful.

Figure 2.1: A  $2 \times 2$  set of elements, networked in a nearest-neighbor topology. Each element communicates with a maximum of four neighboring elements (two in this example). Unconnected I/O lines are available to external devices.

Figure 2.2: A  $4 \times 4$  set of elements. This collection could be made by connecting four copies of the circuit shown in Figure 2.1 along their edges. Each  $2 \times 2$  sub-collection is, in fact, identical to the circuit shown in Figure 2.1.

In general, this will probably be overkill. However, supposing a manufacturing capability where a trillion trillion transistors may be incorporated into a single device, the difference between 10 bits and 10,000 bits of memory per element becomes less critical. And, in fact, we don't need to work with 10-input/10-output devices. The simplest two-dimensional tiling of elements would be based on triangles: each element having three sides, and therefore being connected to three neighbors. If we let each element exchange a single bit with each of those neighbors, the element's truth table would thus be  $2^3$  rows  $\times$  3 columns, for a total of 24 bits. A perhaps more-natural tiling may be achieved with four-sided elements, raising the truth table size to 64 bits. If these elements exchange two bits with each other, the truth table grows to  $2^8$  rows  $\times$  8 columns=2,048 bits: a significant increase in size.

The simplest three-dimensional tiling of elements would be based on tetrahedral elements: each element thus having four sides, and therefore being connected to four neighbors. The complexity is identical to the two-dimensional, four-sided case, with each element requiring 64 bits. A more-canonical element would be a 6-sided cube, requiring a truth table of  $2^6$  rows  $\times$  6 columns=384 bits per truth table. Extending this system to passing two bits between each pair of elements, the truth table size grows to  $2^{12} \times 12 = 49{,}152$  bits per truth table. Note that it's also possible to architect hyper-systems with dimensionality greater than three. Such systems, however, generally fail in their scalability, and thus are not considered herein. Here again, while it may be more convenient to implement elements that exchange multiple bits with each other, or that connect directly to more neighboring elements, doing so is not actually necessary: one can view a collection of two or more elements as acting like a single

composite element. Given the rapid growth of truth table memory requirements, the present work will focus on a relatively simple compromise: four-sided elements, each exchanging a single bit with each of four neighbors. Some consideration will also be given later to six-sided elements, in discussions on three-dimensional circuitry.

Similarly, it will suffice for all elements to be identical to each other, with more-complex elements being built from collections of these simple elements. Note that under this scheme, elements may be used for any of several purposes:

- 1. to implement simple logic functions;

- 2. to implement more-complex logic functions, by working in tandem with other nearby elements;

- 3. to implement memory units such as flip-flops, again by working in tandem with other elements; and

- 4. to act as a wire, i.e., to pass information between non-adjacent elements.

There are additional uses for elements, including using their truth tables as a higher-density memory. This will be described later.